CoWoS、CoPoS、CoWoP傻傻分不清,谁才是下一代最该关注的技术?

随着摩尔定律逐渐逼近物理极限,芯片制程微缩的效益愈发有限,业界正积极寻求新的突破方向,先进封装技术成为近年来最受关注的领域之一。随着台积电 CoWoS 产能持续供不应求,CoPoS、CoWoP 等新技术陆续涌现。这两项技术与 CoWoS 有何差异?何时会投入应用?本文整理相关资讯,为你一一解读。

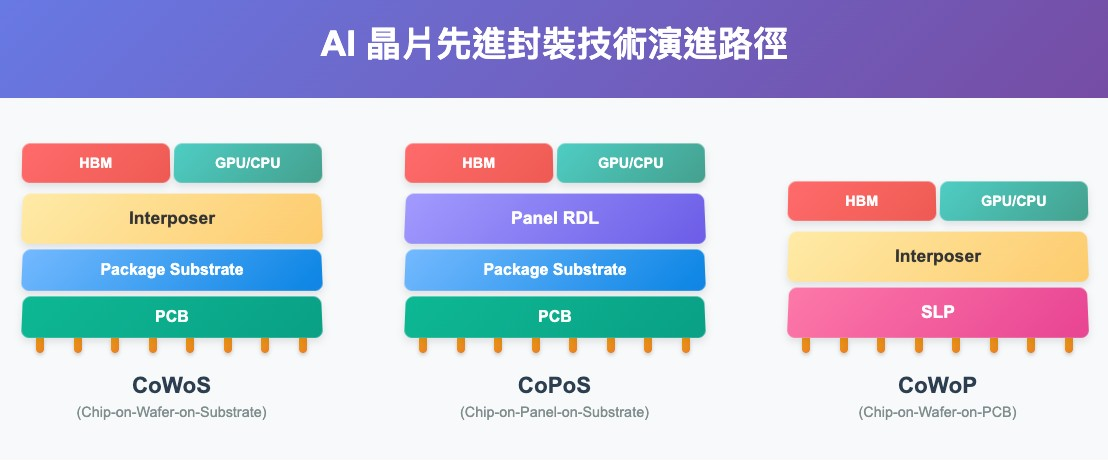

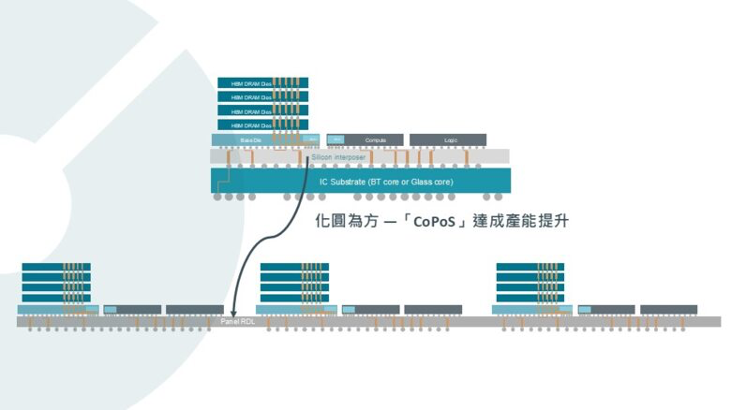

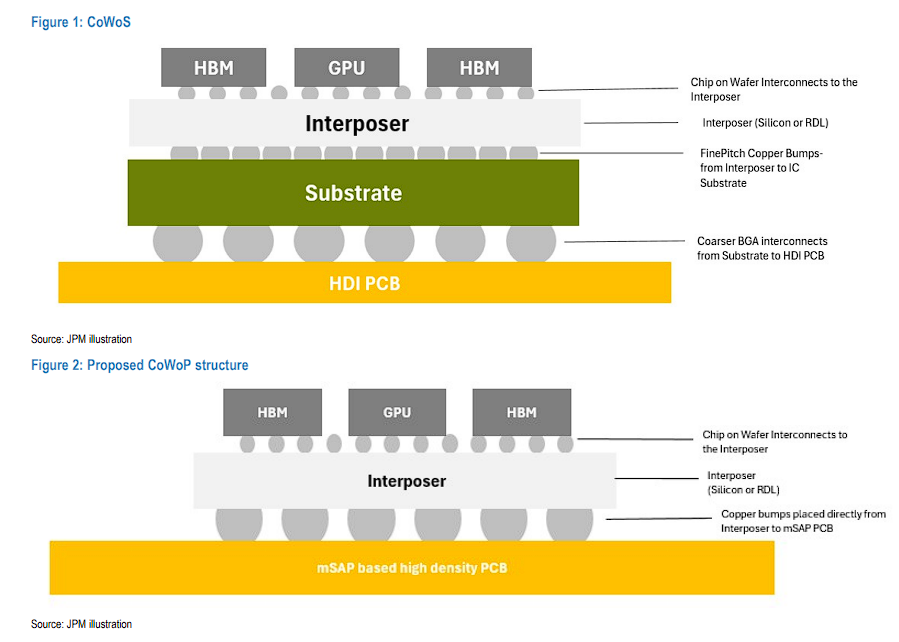

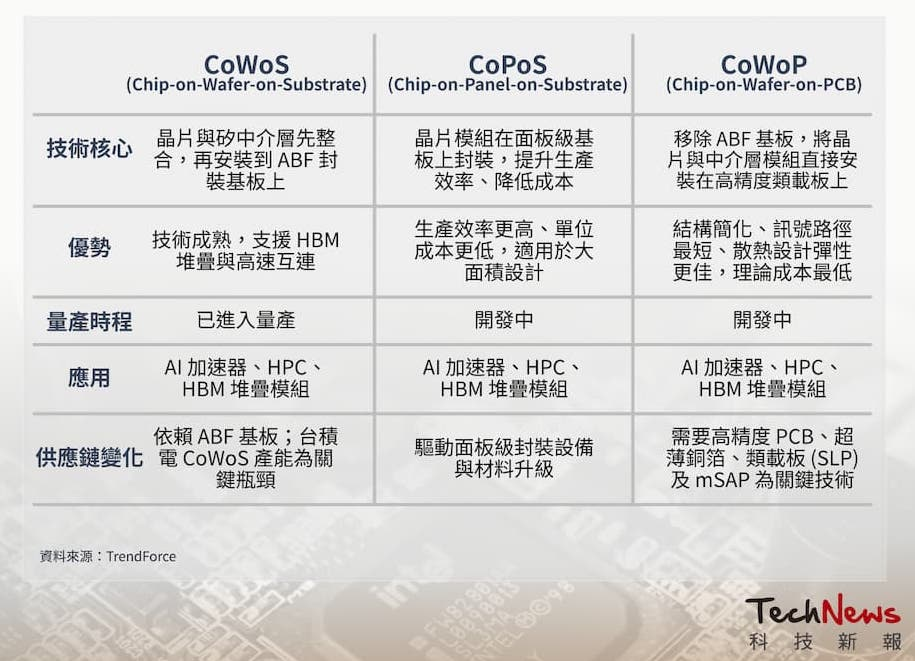

从下图可以看出,CoWoS、CoPoS、CoWoP 的堆叠方式存在差异:CoPoS 主要是将中介层替换为面板 RDL;CoWoP 则通过开发技术含量更高的 PCB 主板,来替代 IC 载板。

接下来,我们详细介绍这三项技术的主要差异。在此之前,先了解这些衍生技术的根源 —— 台积电的先进封装技术 CoWoS。

台积电先进封装技术 CoWoS,细分为 CoWoS-S、CoWoS-R、CoWoS-L

CoWoS 是台积电的 2.5D、3D 封装技术,可拆分为 “CoW” 和 “WoS” 两部分理解。

CoW(Chip-on-Wafer,芯片叠晶圆)指芯片堆叠,WoS(Wafer-on-Substrate,晶圆叠基板)指将芯片堆叠在基板上,因此 CoWoS(Chip-on-Wafer-on-Substrate,芯片叠晶圆再叠基板)的原理是将芯片堆叠后,封装在基板上,最终形成 2.5D、3D 结构,从而减少芯片占用空间,同时降低功耗和成本。

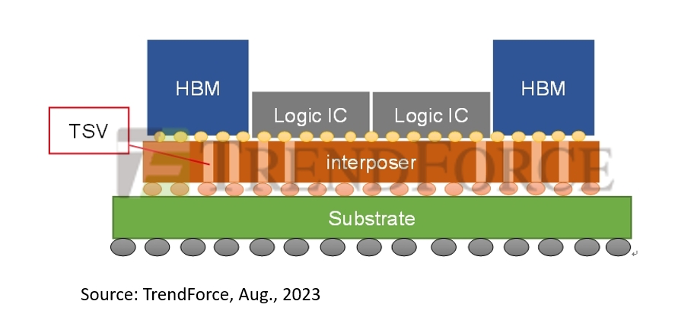

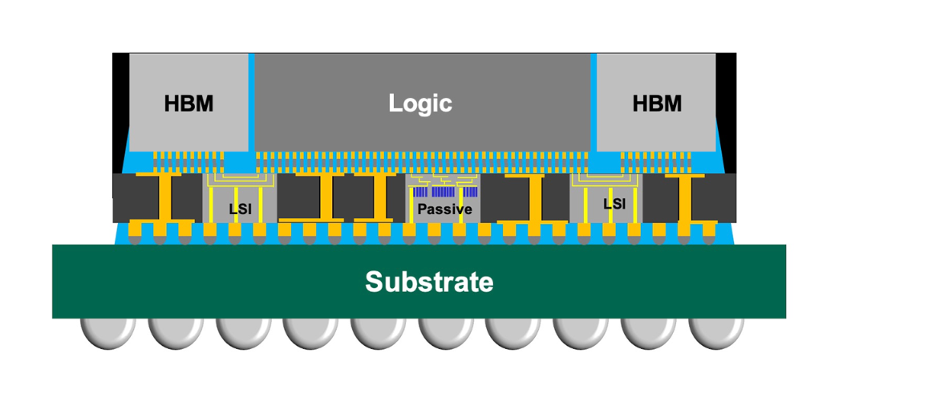

CoWoS 技术先将逻辑芯片与 HBM(高频宽存储器)安装在硅中介层(Interposer)上,通过中介层内部的微小金属线整合不同芯片的电子讯号,同时经由硅穿孔(TSV)连接下方基板,将讯号传导至下层,最终通过金属球(bumps)与外部电路衔接。

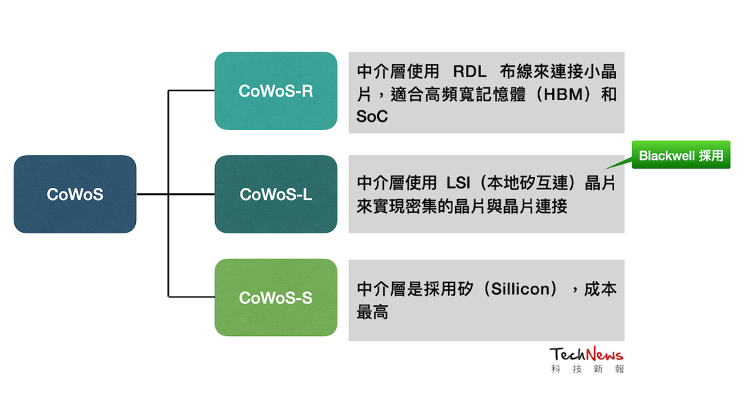

其中,CoWoS 技术又分为 CoWoS-R、CoWoS-L 和 CoWoS-S 三种类型,因中介层材质不同,成本也有所差异,客户可根据自身需求选择。

目前成本最高的是 CoWoS-S,其中介层采用 “硅”(Silicon),也是主流方案,例如 NVIDIA H100、AMD MI300 均采用 CoWoS-S。但 CoWoS-S 由于使用高纯度硅材与 TSV 制程,加工难度较大,且中介层面积受曝光机台限制,封装尺寸上限约为 2500 平方毫米。

▲ CoWoS-S

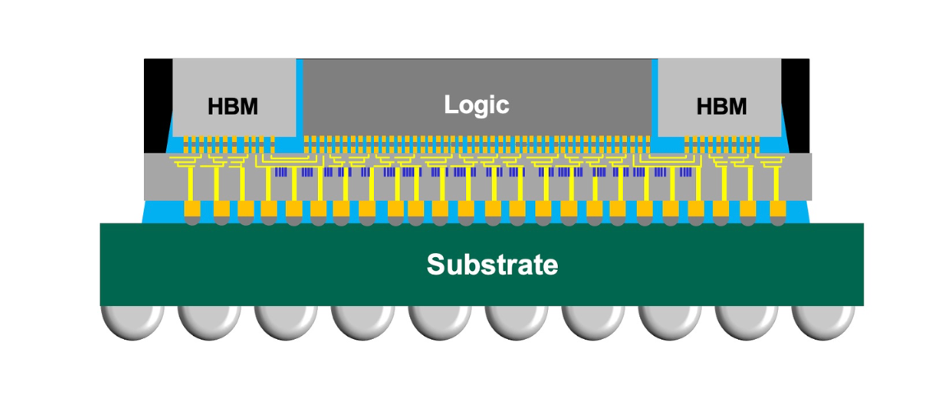

CoWoS-R 采用 InFO 中使用的互连技术,其中介层通过 RDL(重布线层)连接小芯片,支持灵活的封装设计,适用于对成本较为敏感的 AI ASIC 应用、网络通信设备或边缘 AI 领域。

▲ CoWoS-R

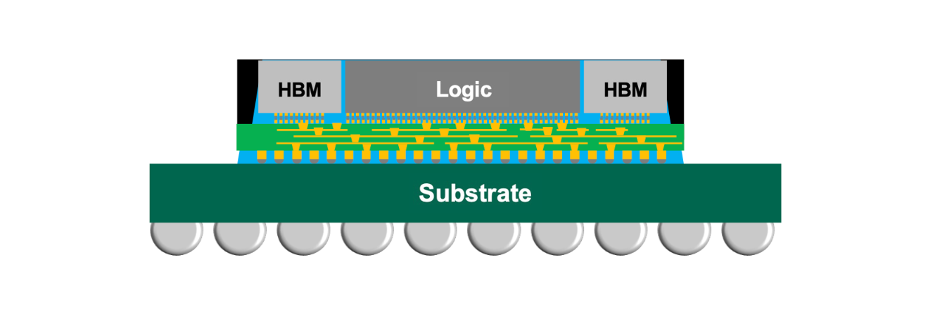

CoWoS-L 的成本介于 CoWoS-S 和 CoWoS-R 之间,中介层采用 LSI(局部硅互连,Local Silicon Interconnect)和 RDL,即局部区域以硅中介层串联芯片,其他区域采用 RDL 或基板,实现密集的芯片间连接,支持多达 12 颗 HBM 存储器的堆叠应用,堪称融合了 CoWoS-S 和 CoWoS-R/InFO 的技术优势。

▲ CoWoS-L

台积电高效能封装整合处处长侯上勇在演讲中提到,由于顶部芯片(Top Die)成本极高,CoWoS-L 相比 CoWoS-R、CoWoS-S 更能满足各类需求,是最佳解决方案,因此会从 CoWoS-S 逐步过渡到 CoWoS-L,并表示 CoWoS-L 是未来技术蓝图的核心。

有趣的是,也有观点认为 CoWoS-L 中的 “L” 代表 “Large”,专为超大型 AI 训练平台与高整合度应用设计,延续 CoWoS-S 架构,同时进一步突破硅中介层的尺寸限制,开发可支持超过 2500 平方毫米的超大面积中介层技术。

▲ CoWoS 技术路线图

CoWoS “面板化”!解决成本与大尺寸芯片翘曲问题

了解 CoWoS 的技术分支后,再来看看 CoPoS 和 CoWoP。

随着 AI 芯片体积越来越大、设计日趋复杂,传统圆形晶圆在面积利用率和封装效率上逐渐显露出局限性,因此开始迈向 “以方代圆”,即用面板(Panel)替代晶圆(Wafer),将芯片排列在矩形基板上,再通过封装制程连接到底层载板,实现多颗芯片的共同封装,这就是所谓的 “CoPoS”(Chip-on-Panel-on-Substrate,芯片叠面板再叠基板)。

▲ CoPoS 示意图

CoPoS 将芯片排列在方形 “面板 RDL 层” 上,取代原先的圆形硅中介层,强化不同导电层与材料间的电路互连布局,提升面积利用率和产能。此外,由于引入玻璃或蓝宝石等新材料,方形尺寸可实现多颗芯片封装、整合不同尺寸芯片,同时支持更大光罩,缓解芯片越大越明显的翘曲问题。

业界分析,CoPoS 是 CoWoS-L 或 CoWoS-R 的 “矩形” 变形方案,将传统 300 毫米硅晶圆改为方形面板设计,尺寸包括 310×310 毫米、515×510 毫米或 750×620 毫米等,目前供应链的研发方向均以台积电发布的规格为基准。不过 CoPoS 初步选定的尺寸为 310×310 毫米。

业界消息称,台积电计划 2026 年设立首条 CoPoS 实验线,目标在 2028 年底至 2029 年间实现量产,首个客户为 NVIDIA。此外,未来 CoPoS 封装主要面向 AI 等高端应用,采用 CoWoS-R 制程的将服务博通,CoWoS-L 则以 NVIDIA 和 AMD 为目标客户。

至于 CoPoS 与 FOPLP(扇出型面板级封装,Fan-out Panel Level Packaging)的差异:前者用于 AI 高端芯片,中介层材料从硅转为玻璃;后者用于 PMIC、RFIC 等低成本芯片的成熟制程,无需中介层,直接通过 RDL 互连。

砍掉封装基板、BGA,CoWoP 能成为 CoWoS 的下一代主要路线吗?

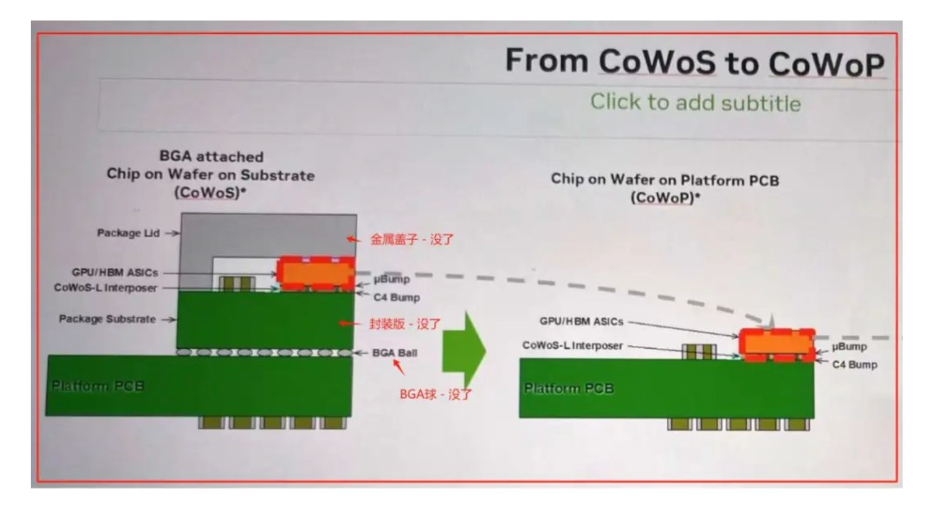

“CoWoP”(Chip-on-Wafer-on-Platform PCB,芯片叠晶圆再叠平台 PCB)是今年新出现的先进封装路线。

目前有消息称,NVIDIA 将在 Rubin GPU 系列的 GR150 芯片上,同时采用 CoWoP 与 CoWoS 两种封装技术。

▲ CoWoP 图示

从图片可知,CoWoS 的结构包括 GPU 等逻辑 IC、HBM、中介层、封装基板(Package Substrate),而实际上,封装基板下方还需通过 BGA(球栅阵列,Ball Grid Array)与 PCB 主板(Platform PCB)连接。

由于 CoWoS 结构的堆叠 “层级过多”,如同不断加盖的楼房,楼层越高,讯号和电力从底部传输到顶部的距离就越长,损耗和成本也随之增加。

因此,CoWoP 计划精简部分层级,即直接去掉成本高昂的封装基板和 BGA,开发技术含量更高的 PCB 主板,使其直接承担高精密度讯号与电源布线,再将 “芯片和中介层” 组合直接安装在 PCB 主板上。这样一来,芯片讯号可直接从中介层传输到 PCB 主板,缩短互连路径,提升讯号完整性和散热性能。

目前 NVIDIA 正在测试 CoWoP 技术,台系供应链企业也证实,替代 ABF 载板的 PCB 主板已正式送样给 NVIDIA 进行测试验证。

▲ CoWoS、CoPoS、CoWoP 技术进展

等等,WMCM 技术又是什么?

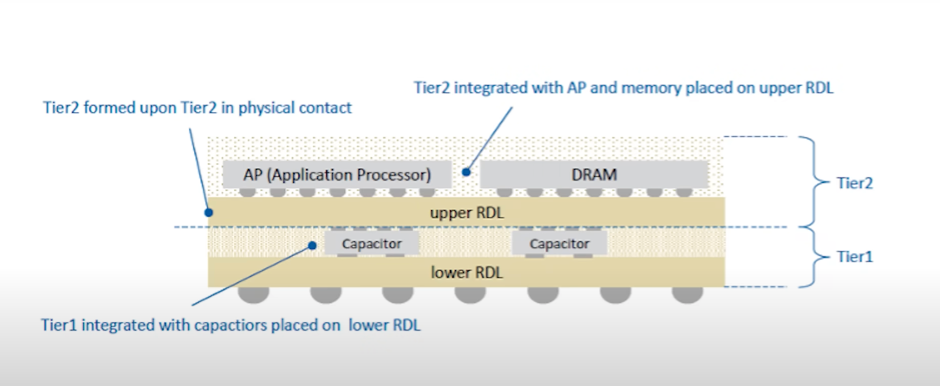

虽然本文主要介绍 CoWoS 及其衍生路线,但今年还有一项 “WMCM”(晶圆级多芯片模组,Wafer-Level Multi-Chip Module)技术同样备受关注 —— 苹果计划在 2026 年推出的 iPhone 18 所搭载的 A20 处理器,将采用这项技术。

据悉,WMCM 是台积电 InFO-PoP 的升级版,由台积电与苹果联合研发,属于 “苹果专用” 的封装技术。

InFO-PoP 是将存储器直接堆叠在移动处理器上方,当存储器容量增加时,散热问题便会凸显。因此,WMCM 通过将 IC 逻辑芯片与 DRAM 进行平面封装,替代传统的上下堆叠方式,以 RDL 取代中介层。

▲ WMCM 示意图

由于 WMCM 在晶圆阶段就完成了 SoC、DRAM 等不同元件的整合,再切割为单颗芯片,因此无需使用中介层或基板来连接晶粒,可改善散热和讯号完整性。

▲ InFO 和WMCM 技术比较

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。