CPO和异构集成,突破互联瓶颈

人工智能的飞速发展,已经超越了传统单片式计算架构的能力边界。行业正转向系统化架构:由大规模 GPU/AI 加速器组成的分布式集群,将作为单一、统一的计算引擎,支撑下一代万亿参数大模型。

共封装光学(CPO)在提升这类架构的互联效率方面拥有巨大潜力,但同时也面临带宽密度不匹配、组装工艺复杂、光纤精准对准等难题。本文探讨下一代AI集群采用 CPO 的机遇与挑战。

向上扩展/向外扩展方案的技术趋势

AI数据中心基础设施主要采用两种截然不同的扩展策略:向上扩展(Scale-Up)与向外扩展(Scale-Out)。

向上扩展(Scale-Up)聚焦于在单机柜内乃至跨机柜构建统一、高性能的计算实体(AI POD)。目前已落地的方案如 GB200 NVL72,通过低损耗铜缆与 NVLink、UALink 或 Scale-Up Ethernet(SUE)等协议,借助 NVSwitch 互联数十颗 GPU(例如 72 颗 B200),使其整体等效为单一逻辑计算单元。

向外扩展(Scale-Out)将数据中心内多个 AI POD 互联,以分布式方式处理超大规模算力任务。这一层通常在长距离(>100 米)场景下使用 InfiniBand 或以太网。

当前向外扩展网络已开始采用 CPO 交换机,以降低远距离传输的信号损耗与功耗。而下一阶段的演进方向,是将硅光引擎集成到向上扩展层,突破铜缆在带宽与传输距离上的固有限制。

光引擎带宽与能效的演进

基于硅光技术的可插拔光模块早在 2018 年就已问世,但光引擎(OE)的部署位置已发生巨大变化:光引擎不再局限于面板可插拔模块,而是可以靠近交换 ASIC(近封装光学),甚至集成到同一封装内(共封装光学 CPO)。这种集成缩短了电学传输路径,带来更高带宽、更低功耗与更强可扩展性。

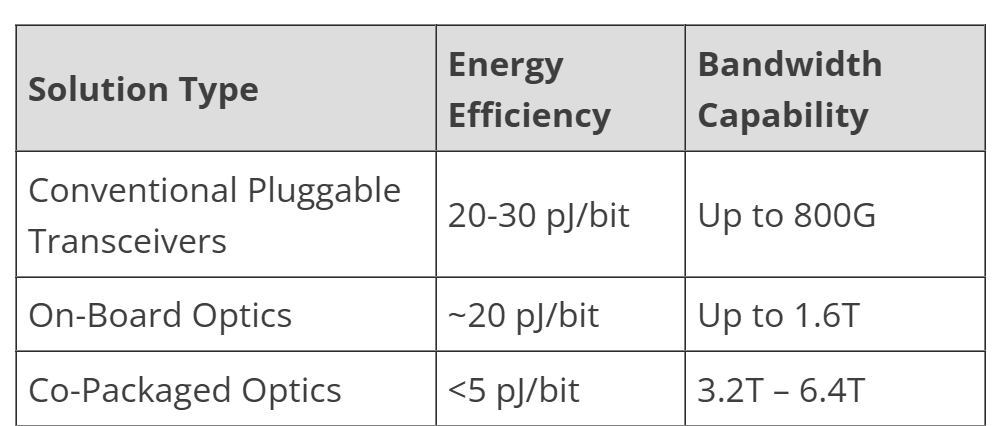

过去五年,集成在光引擎中的电子集成电路(EIC)与光子集成电路(PIC)持续进步,实现了带宽密度提升 64 倍、能效提升 5 倍。传统可插拔光模块功耗约为 20–30 pJ/bit,而 CPO 目标功耗可降至 ~5 pJ/bit,光引擎带宽可扩展至 3.2T~6.4T。

CPO 落地面临的挑战

尽管理论优势显著,CPO 规模化量产仍面临严峻的异质集成挑战。

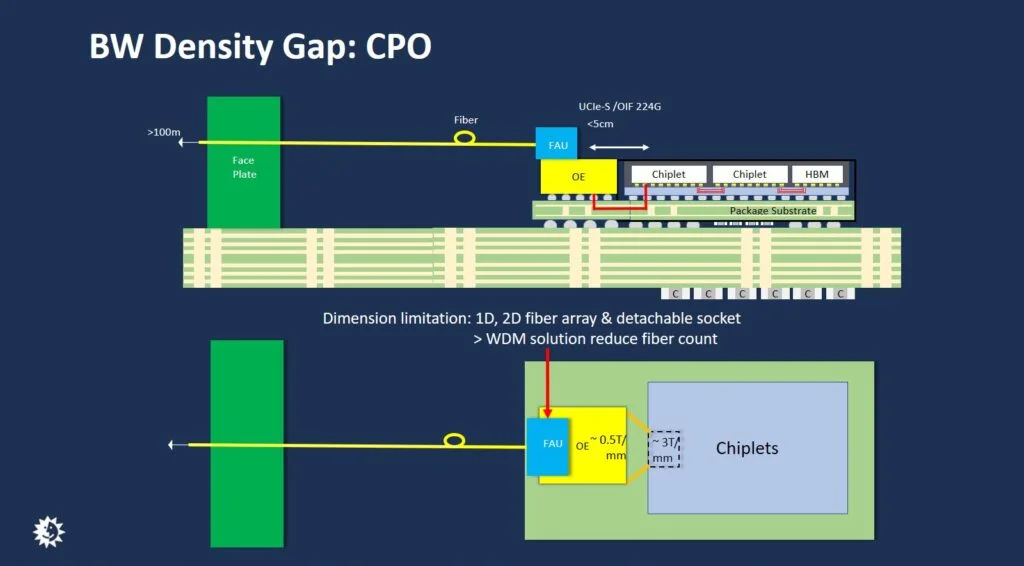

1、带宽密度不匹配

AI小芯片(chiplet)与当前光互联之间存在显著带宽密度差距:采用 UCIe 或 OIF 标准的 AI 小芯片带宽密度约为 3 Tbps/mm,而当前最先进的 CPO 方案仅约 0.5 Tbps/mm,差距达6 倍。

这一差距凸显:必须设计更小尺寸的 PIC,并推动光纤阵列单元(FAU)小型化。由于光纤间距通常超过 100 微米,打造紧凑、可插拔的 FAU 存在实际工程难题。波分复用(WDM)与密集波分复用(DWDM)可减少光纤数量,但如何在温度变化下保证波长稳定性仍是挑战。

2、CPO 组装复杂度高

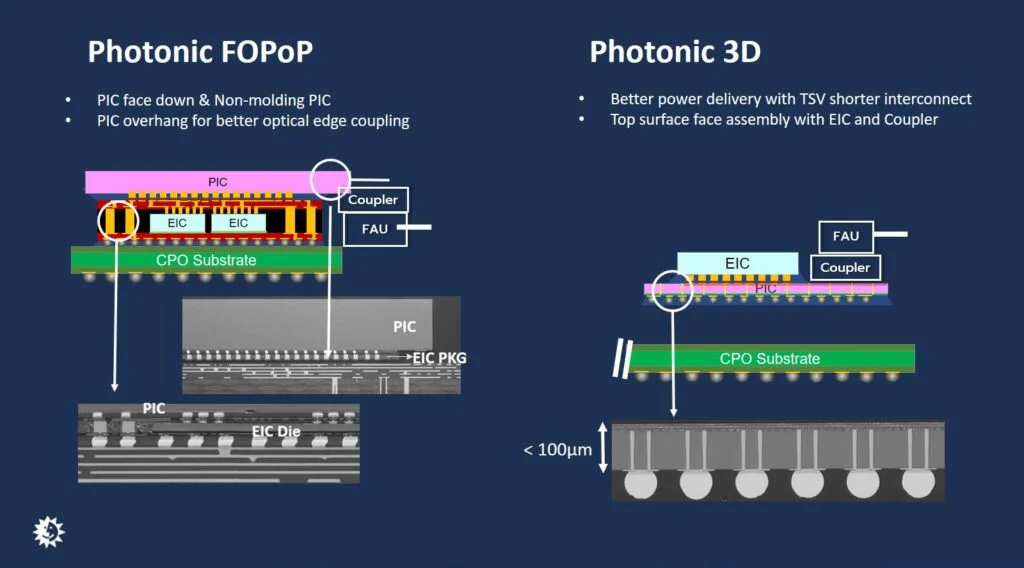

CPO 组装涉及激光器、光学组件、FAU、不同工艺节点的硅基 IC 等多类器件,流程极其精密,尤其是 EIC 与 PIC 的集成。实现更高带宽密度主要有两条技术路线:Photonic FOPoP将 PIC 置于 EIC 上方,采用晶圆级扇出工艺与铜柱实现垂直互联。Photonic 3D将 PIC 置于下方,通过硅通孔(TSV)连接顶部的 EIC。该方案散热更优,支持单通道速率超过 200G,是高性能场景的首选方案。

3、光学对准与耦合

PIC 可实现高精度制造,但其他组件精度难以匹配,易引入制造误差。行业通常采用主动对准(AA),通过实时反馈优化光学耦合,但流程耗时。传统可插拔光模块中,FAU 通过主动对准采用对接耦合或光栅耦合(GC),再用环氧树脂永久固定,单根光纤损坏即无法维修。

为提升可维修性与可升级性,行业正转向可插拔 FAU 方案,但面临亚微米级对准精度、多次插拔重复性与大规模量产(HVM)兼容等难题。一个有前景的方向是:使用晶圆级光耦合器扩大激光光束尺寸,显著放宽耦合公差,支持更具扩展性的组装方式。

4、已知合格光引擎(KGOE)

为保证复杂 CPO 组装良率,必须在最终封装前完成光引擎(OE)的筛选测试。理想方案是双面晶圆级测试:一侧通过自动测试设备(ATE)电接触,另一侧通过可插拔光接口测试。

但该方法不适用于 Photonic FOPoP 结构,因为 EIC 的 I/O 与 PIC 光耦合区位于同一面。在采用 TSV 的 Photonic 3D 结构中,PIC 厚度通常低于 100 微米,需要加固结构才能承受双面测试压力(可插拔接口与 ATE 探针压力可达公斤级)。

展望:CPO 大规模普及之路

通过 CPO 与异质集成扩展 AI 基础设施的前景广阔,但挑战同样艰巨。日月光凭借面向 EIC/PIC 集成的先进 3D 封装技术,走在这一变革前沿。

下一代 CPO 方案需要在带宽密度与能效上实现大幅提升。已知合格光引擎(KGOE) 是保证高良率的关键,要求设计能够兼容 ATE 与可插拔接口压力。

半导体全产业链协同,从 EIC、PIC 设计到封装专家、系统集成商,这些角色对攻克这些挑战至关重要。随着 CPO 技术与封装创新持续推进,半导体行业将有能力满足下一代 AI 在性能、能效与扩展性上的核心需求。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。