直击瓶颈,三星HBM4E供电大改造

三星电子今年王牌产品的HBM4,已经抢先于竞争对手率先向英伟达出货首批量产,气势正盛。而本文要讲的是三星 HBM4 的下一代产品 ——HBM4E。

HBM,我们已经很熟悉了:把多颗 DRAM 垂直堆叠,中间打出2048 个硅通孔(TSV),最大化数据传输通道的芯片。这么堆叠起来的芯片有个致命问题:功耗。人们对半导体的需求很简单:更快处理更多数据。从 HBM3E → HBM4 → HBM4E → HBM5,每一代迭代,容量都在提升,功能也在增加。

随之而来的是芯片内部布线越来越密、越来越多。提到 HBM,大家最先想到的是负责传输数据的 “高速电梯” TSV。但不止如此。随着容量和带宽提升,支撑其运行的供电线路、凸点、金属层也一起增加,彼此间距也变得更密。就好比你房间里本来就有手机、无线耳机、笔记本、平板,现在又塞进电视、扫地机器人、便携屏、投影仪、加湿器、空调,插线板自然越堆越多。

我们可以通过两组数据直观感受供电布线有多密集:

HBM 与中介板、HBM 内部基底裸片与核心裸片之间的微凸点数量

中介板与基板连接的C4 凸点数量

根据三星电子的资料,为 HBM 各部分传输电流的凸点总数,已经从HBM4 13682 个提升到HBM4E 14457 个(C4 凸点 + 微凸点合计)。问题是,凸点数量增加后,想要和前代一样顺畅运行并没那么容易。在同样空间里塞进更多布线,就必须做得更细、更密。这会导致电流密度升高、电阻值上升。

这样一来,驱动 HBM 各部分、最终到达目标位置的电压就会下降。这就是IR Drop(压降)。电压掉了,就得补上,施加比平时更高的电压。然后,发热就开始了。金属温度一升高,电阻会进一步变大,IR Drop 问题更严重。于是又需要更多电,变得更热,电阻彻底失控……最终要么性能下降,要么电路直接断线。

这已经不是信号断不断的问题,而是物理极限在拖后腿,甚至可能让芯片直接报废。带宽固然重要,但支撑一切的基础 ——功耗大战已经打响。如何把芯片内部供电网络设计得更扎实、更高效,正在成为 HBM 行业最核心的课题。

三星电子计划从今年开始量产的HBM4E起,导入全新供电网络。核心是:对 HBM 内部供电网进行分段、分布式改造,相当于一次 “组织架构重组”。

芯片内部的供电网络不是随便铺的,而是以网状(Mesh)形式排布,避免线路互相干扰。资料显示,基底裸片(Base Die)的供电系统由5层网状结构组成。

直到现有产品,基底裸片的供电网络都非常庞大且密集。尤其是 HBM 中靠近基板中介板的供电层(MET4),形成了像蜂窝一样的巨大区块。在下一层,从基板接收电力、向上传输到 HBM 的线路开始逐渐变窄。

这种设计虽然因为有多条路径供电而具备稳定性,但布线一旦复杂,问题就来了:在通往下层狭窄通道的位置,入口突然收窄,就像车道变少引发堵车一样,出现瓶颈。而且起点到终点的距离很长,IR Drop 问题会大幅加剧。

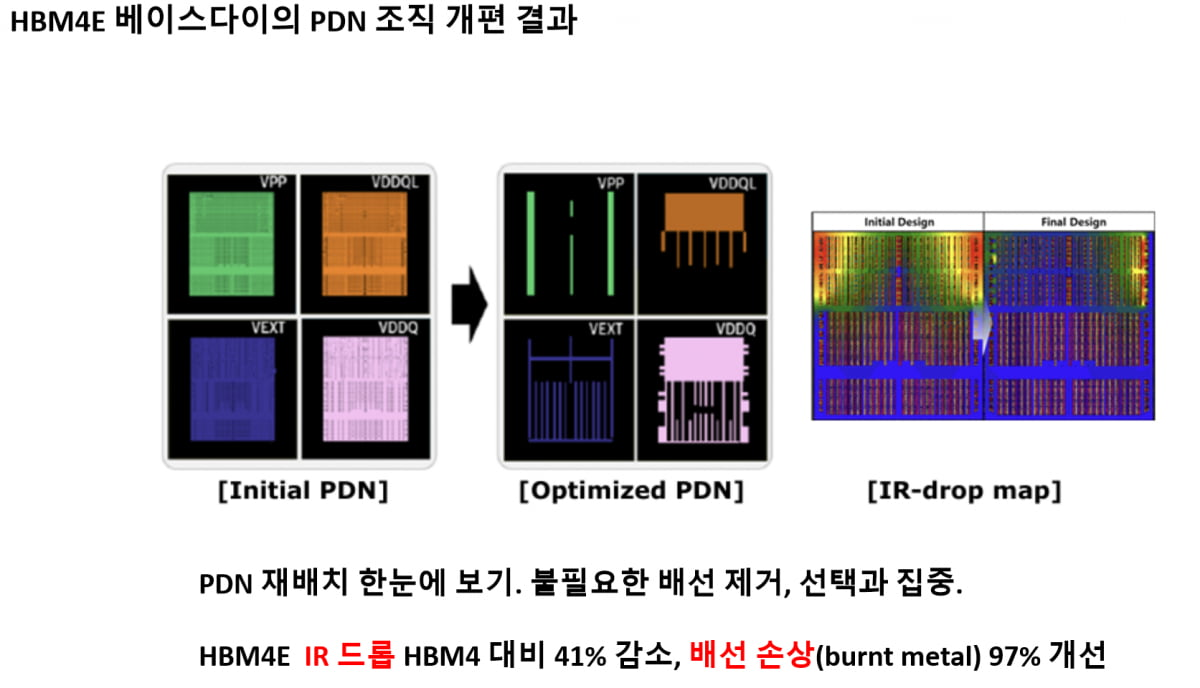

为解决这一问题,三星对PDN 进行了精细化拆分。从改进后的 MET4 层可以看到,巨大的布线区块被拆成仅 4 个小块。在下一层也增加了布线区块,把瓶颈最小化。至少从观感上,每个凸点到目标位置的线路都更直接、更少冗余。

从鸟瞰视角看,这套优化后的 PDN 实现了精准的取舍与聚焦。三星方面表示HBM4E 金属电路不良率较 HBM4 减少 97%;IR Drop 压降问题改善 41%。IR Drop 降低,电压裕度就会变好,既能实现更高速度,芯片整体可靠性也会提升。

不过,这种精细化分布式供电设计,也可能拉长开发周期。三星公开的资料显示:过去哪怕只移动一个凸点,要解决连锁反应问题需要12 周;如今通过自动布局布线工具,时间压缩到了2.5 周。推测是与新思科技、其收购的 Ansys 等 EDA 自动化设计工具巨头紧密合作的成果。

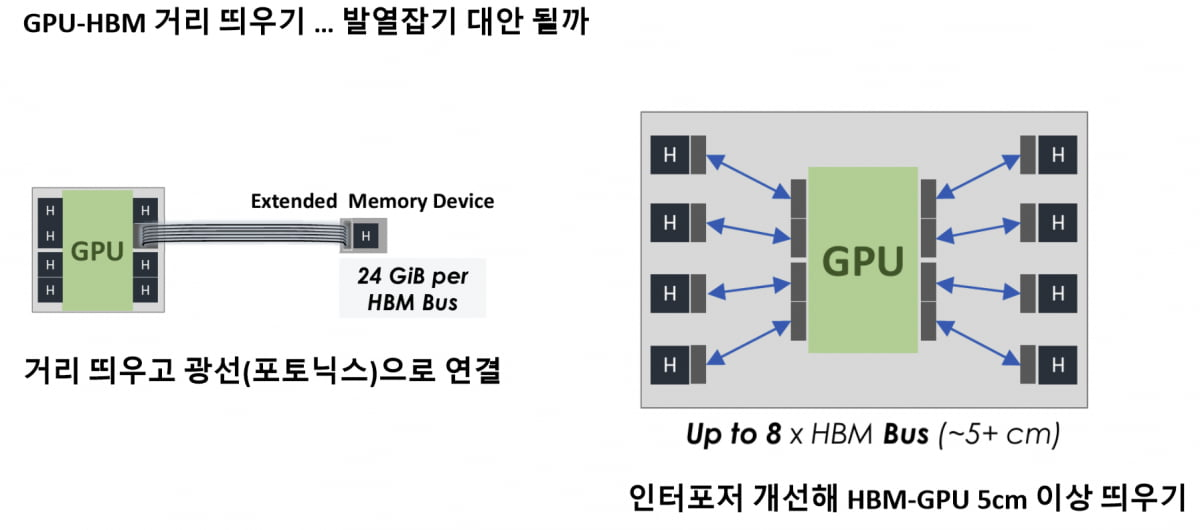

如果连分布式供电都摸到极限,AI 芯片的发热问题仍无法解决,该怎么办?三星在这次演讲中抛出了多个新思路。核心是:将布线高度复杂的 HBM 与 GPU 拆分离(Disaggregation)。

首先是一个非常新颖的方案:用光子(Photonics)连接 HBM 与 GPU。光子,简单说就是光。理论上,传统铜布线每秒只能传输 GB 级数据,而光子可以达到 TB 级,速度提升约1000 倍。

这个思路是:用光学技术解决 HBM 与 GPU 因物理距离拉长带来的延迟问题。

三星还提出,仅靠改进基板布线技术,就能拉开 HBM 与 GPU 的距离,从而改善发热。现在 HBM 和 GPU 几乎是贴在一起的,而他们想把距离拉开到5 厘米以上来解决问题。

HBM 行业里,大家总在聊速度、堆叠层数这些让人兴奋的数字。但如果能关注到这些数字背后的功耗大战,你就能更全面地看懂芯片技术趋势。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。