面向可持续AI的全环绕栅极(GAA)技术

从FinFET向GAA晶体管技术的转型,是逻辑器件发展历程中的一个关键转折点。这一变革既是受物理尺寸极限的驱动,也是为了满足AI领域飞速增长的计算需求。

当半导体工艺进入3nm 以下节点时,传统 FinFET 结构在静电控制、性能扩展与能效方面开始面临根本性挑战。GAA 晶体管的出现,绝非一项可选的技术增强,而是支撑未来逻辑架构、实现可持续 AI 计算的必要基础,这一点毋庸置疑。

FinFET 的推出是为了克服平面 MOSFET 的不足,它通过三维鳍式结构提升了有效沟道宽度与静电完整性。然而,在持续激进的微缩过程中,FinFET 的固有局限逐渐暴露。随着鳍片宽度不断缩小,寄生电阻上升,载流子迁移率因量子限制效应与表面粗糙度散射而下降。此外,FinFET 的三面栅结构在先进工艺节点下难以充分抑制短沟道效应。这些问题共同制约了进一步的尺寸微缩,尤其是在标准单元高度接近140–160 nm区间时。

而GAA晶体管从根本上解决了这些难题:它采用栅极完全包裹沟道的结构,实现更优异的静电控制。这种全包围栅结构能够实现更陡的亚阈值摆幅、更低的漏电流,并在极小尺寸下仍具备良好的短沟道抑制能力。由此,GAA 架构可将标准单元高度再次微缩至100 nm 及以下,重新恢复了在FinFET后期已趋于停滞的性能与功耗缩放能力。这一优势推动全行业将GAA确立为3nm 以下节点FinFET的继任技术。

除静电性能外,GAA 器件还带来了前所未有的设计灵活性。FinFET 需要依靠离散的鳍片数量来调整有效沟道宽度,而 GAA 晶体管可对纳米片宽度进行连续调节。这一特性使设计人员能在同一工艺节点内精细平衡速度与功耗。更宽的纳米片适用于高性能计算与服务器应用,更窄的纳米片则可降低功耗,面向移动与 AI 负载。这种覆盖宽范围速度–功耗区间的能力,使 GAA 尤其适合异构系统与面向特定应用的优化。

生成式AI与大语言模型的兴起,进一步提升了 GAA 技术的重要性。AI 工作负载对算力提出指数级增长需求,推动系统向千万亿次级(petascale)、百亿亿次级(exascale)性能迈进。与此同时,全球数据中心功耗预计将大幅上升,引发能源可持续性担忧。GAA 晶体管直接缓解了这一矛盾:它能实现更高的每瓦性能,并支持更高的 SRAM 密度。片上存储密度的提升可减少片外数据搬运,改善数据局部性,降低高速互联带来的能耗成本。

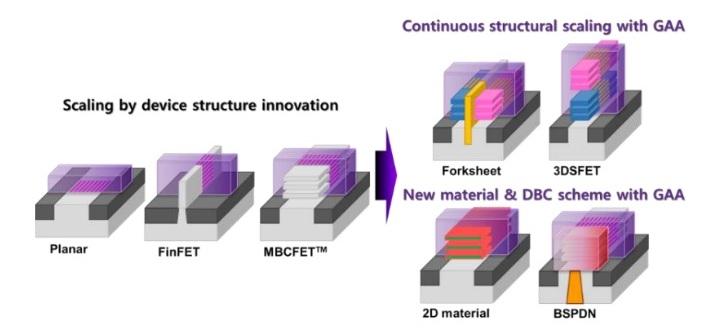

至关重要的是,GAA 还将成为未来晶体管创新的结构平台。Forksheet FET、3DSFET等架构均直接基于 GAA 理念发展而来,在保留其静电优势的同时实现进一步的面积微缩。若与背面供电网络(BPDN)结合,这些先进结构可带来更优的布线效率、更低的电压降与更强的整体性能。这些创新共同奠定了 GAA 作为 “后 GAA 时代” 逻辑技术基石的地位。

向GAA技术的转型,标志着半导体设计的一次根本性变革。GAA 不仅是 FinFET 的替代品,更是一个可扩展、高灵活、高能效的平台,足以支撑未来逻辑架构与可持续 AI 的发展。当器件微缩持续面临物理与功耗限制时,GAA 的成功落地,将决定整个行业能否满足下一代计算在性能、能效与社会需求上的挑战。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。