功率半导体中热性能的芯片级优化

先进的宽禁带(WBG)和超宽禁带(UWBG)半导体中日益增加的功率密度,使得热管理优化成为必要。虽然封装起着关键作用,但为了充分利用这些器件的优势,芯片级(die-level)的改进同样重要。在本文中,我们将讨论热管理优化涉及的一些关键方面,并以氮化镓(GaN)和碳化硅(SiC)为例进行说明。

功率半导体的热导率

功率器件或模块的热性能往往会限制功率转换系统的整体成本、尺寸和性能。半导体的热导率(k),单位为W/m・K,是一种基本的材料属性,它不仅取决于本征材料,还取决于其掺杂、应变 / 应力以及晶体取向。

此外,相邻层之间的界面效应也会产生重大影响。Boteler 等人的一项分析比较了半导体、芯片厚度及其散热与由此产生的器件结温(Tj)升高之间的相互作用。结温(Tj)及其在应用中的循环决定了许多重要指标,例如器件性能、可靠性和寿命。通常,较高的 Tj 会导致关键参数退化,例如器件的导通电阻、漏电流和寿命,因此数据手册中会设定一个上限(例如 125°C)。

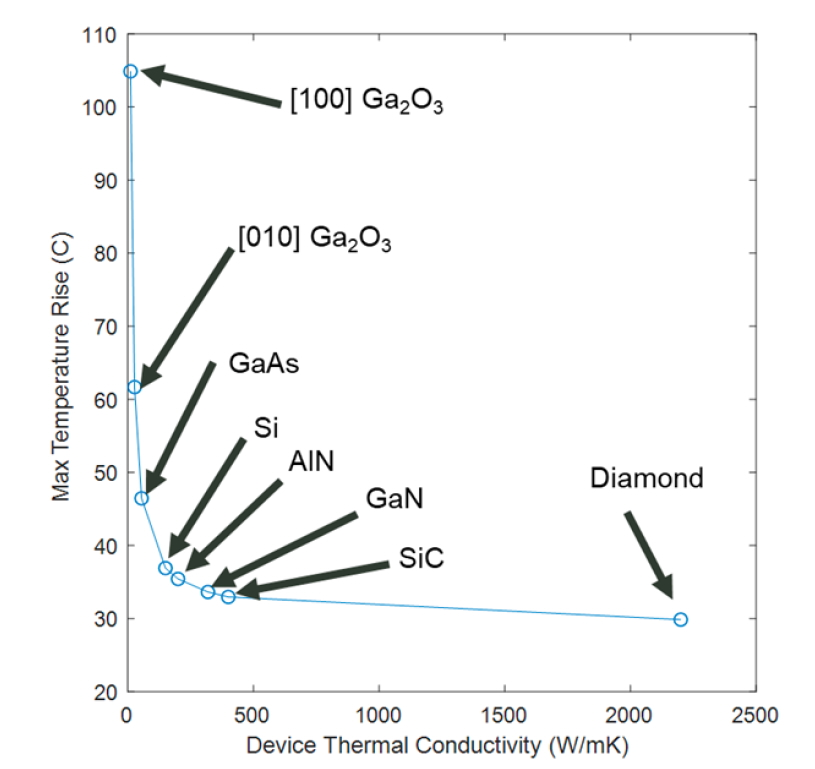

不同功率半导体的最大器件温升与热导率的关系

具有良好 k 值的半导体(如金刚石和 SiC)显示出非常小的 Tj 升高。在 k 值为 150 W/mK(硅)和 400 W/mK(SiC)之间的曲线上可以看到一个拐点。热导率较差的材料(如超宽禁带材料氧化镓)显示出显著的 Tj 升高。这可能会直接抵消该材料可以提供的任何其他与材料相关的优势,并表明需要显著的封装改进才能使其成为可行的选择。

该研究还表明,当传热系数高于 50,000 W/m²K 时,Tj 对散热器相对不敏感。传热系数较低的散热器会显著导致整体 Tj 升高;也就是说,在这种情况下,器件结到壳的热阻并不是一个足够的度量标准。

因此,这对冷却要求设定了一个实际的、足够的限制。由于 k 值低于约 150 W/mK 的半导体材料在 Tj 升高中起着重要作用,减小此类半导体的芯片厚度可以显著改善热性能。请注意,即使是像 SiC 这样的高 k 材料,在衬底电阻起重要作用的应用(如肖特基二极管)中,也倾向于使用更薄的芯片。

针对热性能的芯片设计优化

Tj 的升高取决于几个因素。在最基本的层面上,这可以表示为:Tj = Tj = (RθJC + RθCA) × Pdiss + Ta

其中 RθCA是壳到环境的热阻,Ta 是环境温度,Pdiss 是在转换过程中耗散或热损失的功率。

Pdiss 是传导损耗和开关损耗的组合,可以表示为:

Pdiss = Pcond + Psw

传导损耗 Pcond 取决于器件的比导通电阻RDS(on)-SP,以及路径中的其他电阻,例如由键合线、焊料 / 烧结 / 连接过孔和金属走线产生的电阻。

比导通电阻(RDS(on)-SP),单位为欧姆・平方毫米(Ω・mm²),是一个定义给定器件面积下实际RDS(on) 有多低的指标。在这一重要指标上,WBG 器件比传统硅器件有一个数量级的改进。该参数取决于多个因素,包括温度、材料特性(如载流子迁移率)和器件设计。

随着器件击穿电压(BV)额定值的增加,器件必须扩大尺寸以适应耗尽区上的压降。这相应地增加了 RDS(on)-SP。与横向器件(如 GaN HEMT)相比,垂直器件(如SiC MOSFET)在 BV 额定值增加时,RDS(on)-SP 的增加代价较小。

对于满足给定电流额定值和所需 BV 额定值所需的给定芯片尺寸 “A”,最低的 RDS(on)-SP 会导致最小的传导损耗(I² × RDS(on))。随着 A 的增加,Psw相应增加。

Pcond 和 Psw 的相对贡献可能因应用而异。例如,在接近满载下运行的低开关频率电机驱动应用将有较高的 Pcond 比例,因此,较低的 RDS(on)-SP 特别有益。

电场和电流分布在 Tj 升高中起着主要作用。由于电流流过更大的横截面积,垂直器件具有更均匀的热分布。这些器件中的电场分布也更均匀。

在像 HEMT 这样的横向器件中,栅极 - 漏极边缘和表面传导处会产生高电场,这增加了局部热点的可能性。声子散射的增加导致了热量的产生。降低栅极边缘电场的场板是 HEMT 热设计优化的关键部分。

半导体界面可能是原子无序和位错缺陷的区域。这些增加了载流子散射,导致热边界电阻(TBR)增加。如下文详细所述,具有低缺陷的高质量异质结可改善 TBR,这在 GaN HEMT 制造中尤为重要。

掺杂和应力/应变也会导致载流子散射增加和 Tj 升高。轻掺杂通常不会改变声子热容和晶格结构;然而,重掺杂会缩短声子寿命并降低热导率。因此,这会在电导率和热导率之间产生权衡。

热设计的一个有趣方面是在短路或雪崩等应力条件下的管理。在短路条件下,器件温度升高会导致器件失效。降低这种风险可能涉及增加器件 RDS(on) 的设计,这在正常工作下会牺牲 Tj 的升高,以便在短路条件下提供余量。

雪崩期间的电场管理需要仔细设计结终端。这确保了雪崩主要发生在器件的有源区,而不是容易因热点而失效的边缘。

现在让我们看一下 GaN 和 SiC 器件热设计改进的具体示例。

GaN HEMT热设计

Akshay Gangadharan Nambiar 的一项有趣研究考察了各种 GaN HEMT 衬底。典型的功率 HEMT 是使用 GaN-on-silicon(硅基氮化镓)技术制造的。

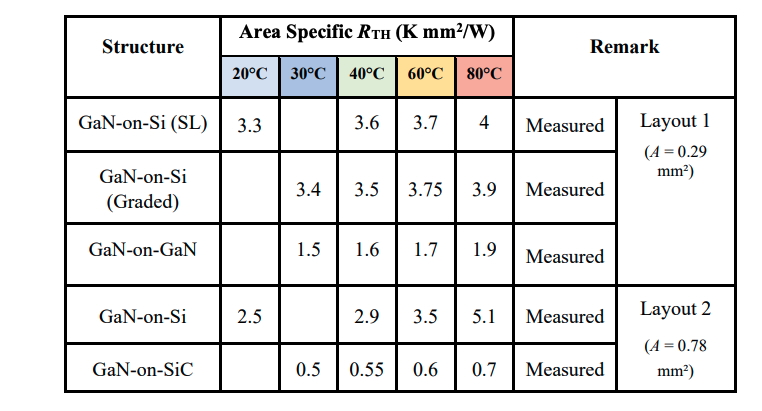

各种 GaN HEMT 技术的测量和计算热阻。

该图中的Layout 1 和2指的是两个集成温度测量电路。使用 GaN-on-GaN(同质外延氮化镓)可显著降低热阻,因为可以避免晶格匹配所需的界面层(如氮化铝)。SiC 较高的热导率反映在 GaN-on-SiC(碳化硅基氮化镓)技术的热阻改善上。

对于 GaN-on-silicon 技术——或其他与衬底存在晶格失配的技术——可以使用渐变铝镓氮(graded aluminum gallium nitride)层。较厚的渐变层虽然对降低缺陷率更好,但会显著增加整体热阻。

薄的阶梯渐变层(step-grade layer)可能是首选,特别是如果使用高导热衬底的话。一项研究表明,使用薄界面层对热导率的好处可以克服位错缺陷增加的缺点。这在 GaN-on-diamond(金刚石基氮化镓)技术中可能很显著。

Akash Systems GaN-on-diamond 技术基于在 GaN 外延背面上生长 CVD 金刚石衬底,已证明其 Tj 比 GaN-on-SiC 低 70°C 以上。

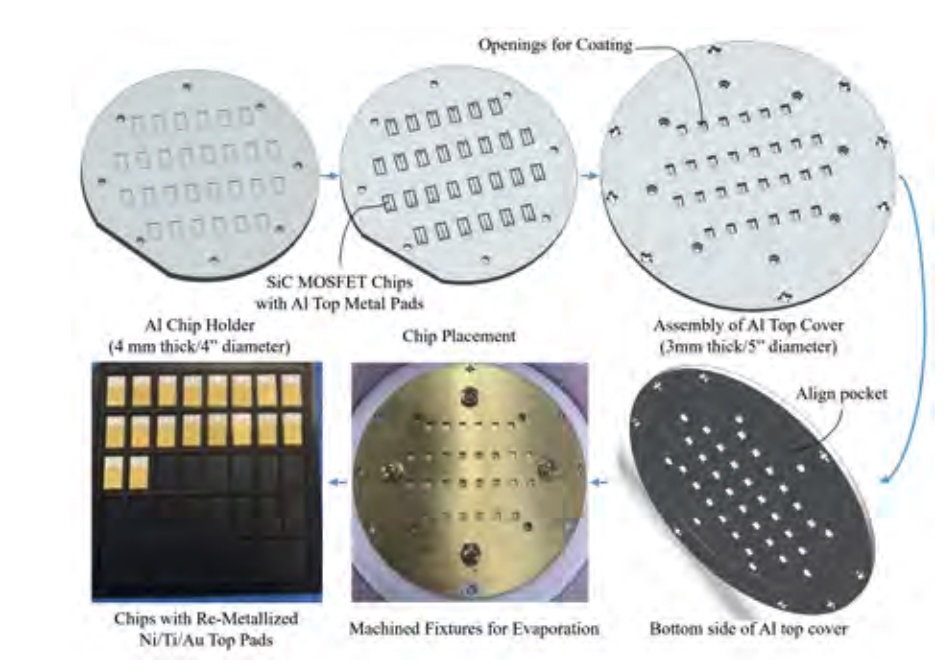

用DS的SiC MOSFET焊盘修改

使用烧结金属化(例如银或铜)连接 SiC MOSFET 的顶面和底面,可实现功率模块的双面冷却(DSC),从而将其功率处理能力提高 50% 以上。

为此,需要修改器件顶部(源极)的铝焊盘,在焊盘上放置贵金属(如金)。为了获得足够的面积和间距,可能需要进一步重新设计焊盘布局。

烧结DSC工艺流程在大功率模块中特别有用

阿肯色大学的 Yuxiang Chen 及其同事最近展示了他们的焊盘修改方法:使用电子束蒸发钛 / 镍 / 金堆叠,并进行优化的 325°C、三分钟后退火,以确保工艺均匀、高产且不影响 MOSFET 特性。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。