汽车电子,从单片SoC走向多芯片设计

受算力需求攀升、功能安全要求提高以及向可扩展半导体架构转型等因素驱动,现代汽车电子正经历快速变革。支撑这一变革的最重要技术突破之一,便是多芯片系统集成方案的普及。

多芯片设计是指将多颗同质或异质半导体裸片集成于单一封装内,以实现更强的可扩展性、更高性能与更好的可靠性。这一架构演进对高级驾驶辅助系统(ADAS)、自动驾驶及数字座舱应用尤为关键,传统的单片式SoC设计已难以满足日益增长的需求。

汽车应用环境对电子器件提出了极为严苛的工作条件要求。器件必须耐受振动、极端温度、湿度与电磁干扰,同时满足功能安全标准。此外,车辆需在极少维护的情况下可靠运行 10–15 年。随着汽车自动驾驶等级提升,算力需求呈指数级增长。更高等级的自动驾驶需要复杂的处理链路,包括 CPU、GPU、AI 加速器、数字信号处理器及高带宽存储子系统。这些需求往往超出单片芯片制造的实际极限,进而推动行业向模块化多芯片架构转型。

多芯片设计具备多项技术优势。首先,它提升了可扩展性,设计人员可复用成熟裸片并以不同组合方式集成,相较于为每款产品重新设计全新单片芯片,能大幅缩短开发周期并降低风险。其次,将功能拆分至更小尺寸裸片可提升制造良率。大尺寸单片裸片缺陷率更高,而小裸片能显著提升有效芯片产出概率。第三,多芯片封装支持异质集成,设计人员可将采用不同工艺节点的组件组合使用,例如将先进数字逻辑芯片采用前沿工艺,模拟或 I/O 电路采用成熟工艺,从而在功耗、性能与成本间实现最优平衡。

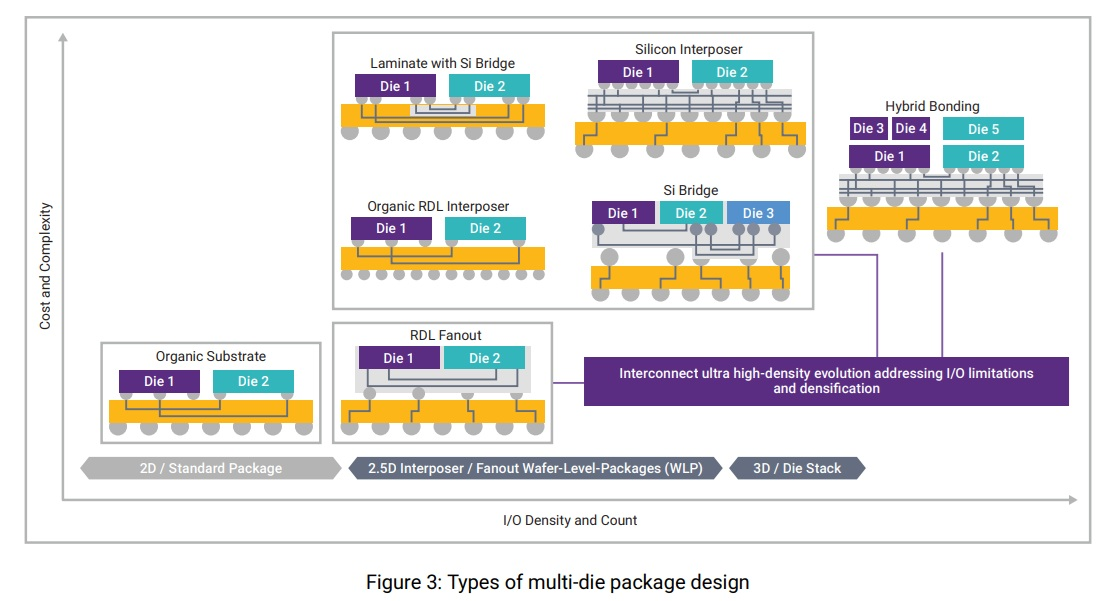

此外,其核心优势还在于互联性能提升。封装内部的裸片间通信,相比传统 PCB 板上的芯片间通信,带宽显著更高、时延更低。这对自动驾驶中的AI推理运算、传感器融合及高清摄像头处理尤为重要。2.5D 中介层、3D 堆叠与微凸点互联等先进封装技术可实现极高 I/O 密度,支持将存储器堆叠在计算裸片上方,或将功能模块分布至多颗裸片,同时维持高数据吞吐量。

安全性与可靠性仍是汽车多芯片系统的核心考量。ISO 26262 等标准要求具备故障检测、冗余设计与故障安全机制。多芯片架构也带来额外挑战,包括裸片间互联监测、热热点管控及封装级可靠性保障。为应对这些问题,设计人员引入硅生命周期管理(SLM)技术,包括工艺、电压与温度传感器、纠错编码及健康监测电路。这些机制支持预测性维护与现场诊断,确保故障及早被发现并处理,避免危及行车安全。

区域架构与软件定义汽车等新兴整车设计趋势,也进一步推动了多芯片架构的应用。现代设计不再将大量小型电控单元分散布置于车身,而是将算力资源集中于高性能处理器。多芯片平台可灵活扩展算力,覆盖从入门级驾驶辅助到完全自动驾驶的各级别车型。厂商可通过将基础裸片与可选 GPU 或AI加速器裸片组合,打造芯片系列,实现高效的产品差异化。

尽管优势显著,多芯片设计也带来了工程复杂性。设计人员需谨慎划分功能、优化互联拓扑,并验证多裸片间的系统级行为。更高功耗密度使热管理难度加大,验证流程需同时兼顾裸片级与封装级交互。不过,电子设计自动化工具的进步与标准化互联协议的普及,正让这些挑战逐步可控。

多芯片半导体集成正成为下一代汽车电子的基础技术。凭借可扩展算力架构、更高良率、异质集成能力与更强可靠性,多芯片设计有效弥补了单片式 SoC 的局限。随着汽车持续向自动驾驶与软件定义功能演进,多芯片系统将在支撑未来汽车平台所需的性能、安全与灵活性方面发挥关键作用。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。