主流的SiC MOSFET架构

SiC MOSFET满足了电力电子行业对更高效率、更高功率密度以及在极端温度下运行的要求,其应用领域涵盖电动汽车(EV)牵引逆变器、可再生能源系统和工业电源。本文将深入讨论不同的SiC MOSFET架构方案。

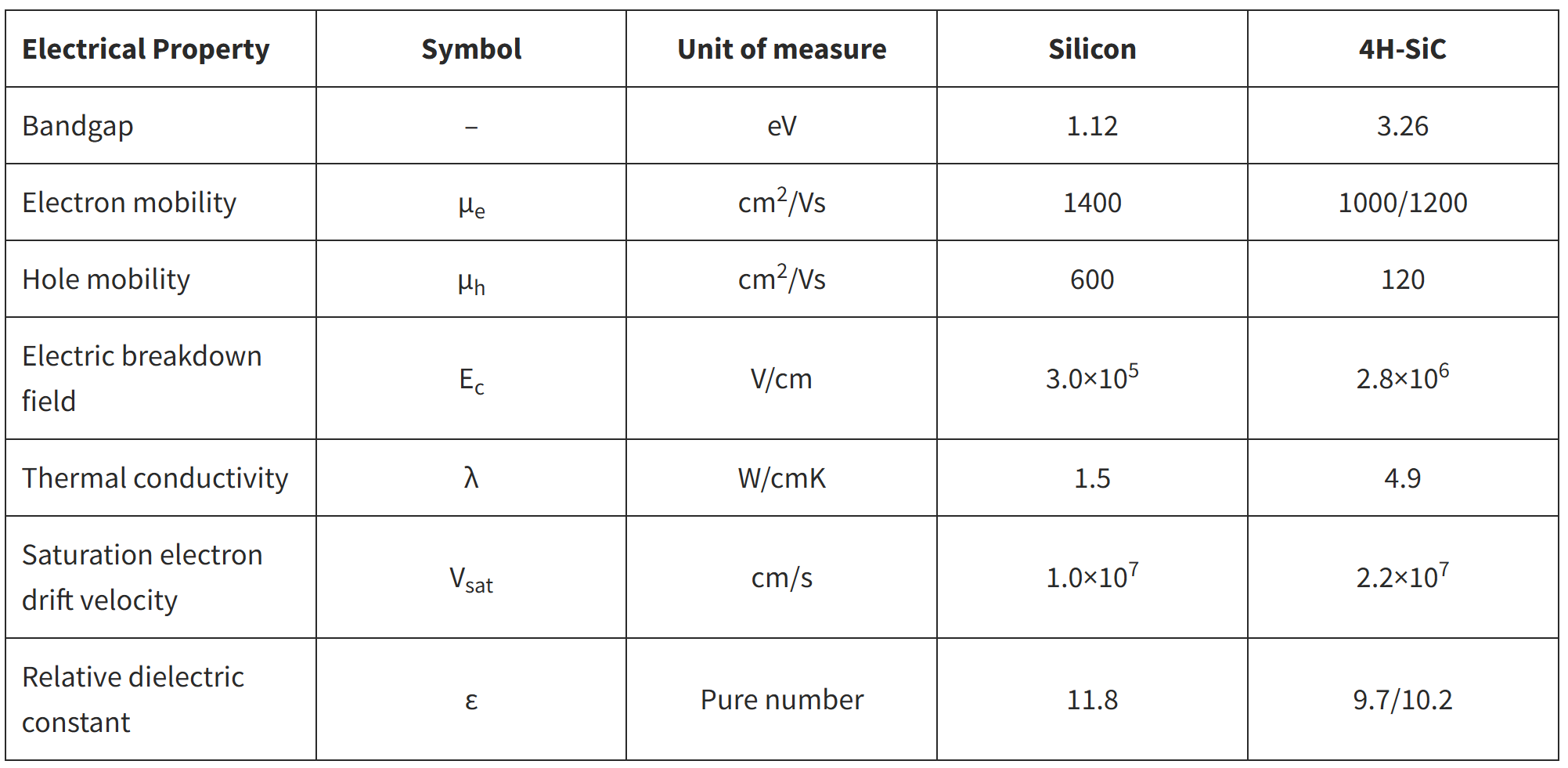

MOSFET作为开关器件在电力电子领域应用广泛。作为一种宽禁带半导体,SiC 相比硅具有多项优势,包括更高的击穿电场、更高的导热率、更低的导通电阻、更快的开关速度、更高的工作温度。

SiC之所以能实现比硅更低的导通电阻,是因为其更高的击穿电场允许使用更薄、掺杂更重的漂移层。这降低了导通损耗并提高了功率密度,弥补了 SiC 沟道迁移率较低的劣势,使其非常适合高压电力电子应用。更薄的层也意味着更小的结电容,从而在开关过程中实现更快的充放电,即更高的开关频率。

这些优势转化为更小、更轻且更高效的电源系统。然而,MOSFET本身的架构在发挥这些材料优势方面起着至关重要的作用。下文会介绍几种目前业内比较主流的SiC MOSFET架构。

平面型MOSFET (Planar MOSFET)

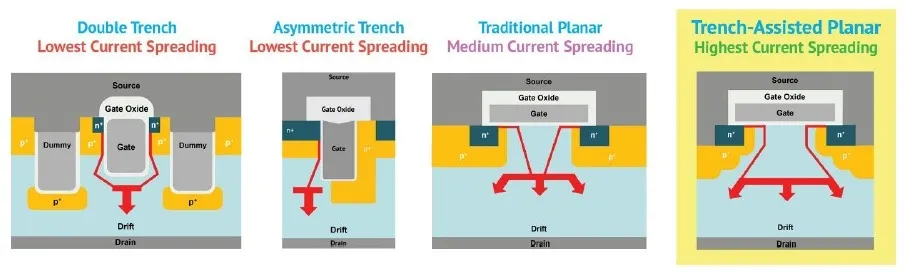

平面型SiC MOSFET架构是第一代商用 SiC 功率器件,由于其可制造性,大多数公司仍在继续使用。在这种结构中,栅电极放置在 SiC 晶圆表面,通过水平沟道控制电流。

该架构的主要优势在于制造工艺更简单、技术更成熟,与更复杂的架构相比,能实现更高的良率和更低的生产成本。此外,由于栅氧化层生长在平坦表面上,更容易控制其质量和厚度,从而避免了可靠性方面的隐患。

其主要挑战在于,由于相邻单元之间区域存在结型场效应晶体管(JFET)效应,且电流通过器件的路径较长,导致沟道比导通电阻较高。这种固有限制降低了功率密度并增加了导通损耗,尤其是在较高工作温度下。

尽管存在这些挑战,平面型SiC MOSFET仍被广泛使用,特别是在成本和成熟度为优先考量的应用中。

沟槽型MOSFET(Trench MOSFET)

在沟槽架构中,栅电极垂直嵌入 SiC 衬底中,沿沟槽侧壁形成垂直沟道。该拓扑结构旨在显著提高沟道密度,消除影响平面型器件的 JFET 电阻。

由于寄生电容减小,这使得比导通电阻更低,并改善了开关特性。此外,这种结构提供了更高的单元密度,意味着可以在相同的硅面积内封装更多的晶体管,从而实现更小、更高效的芯片。

该结构的主要挑战在于电场管理。当器件处于阻断状态时,极高的电场会集中在栅极沟槽的底部和尖角处。这种电场集中可能会影响器件的长期可靠性,因为栅氧化层在这些应力条件下可能会随时间推移而退化。

这种可靠性问题最初阻碍了沟槽型SiC MOSFET的广泛采用。因此,该架构虽然提供了显著的性能提升,但需要先进的工艺控制。

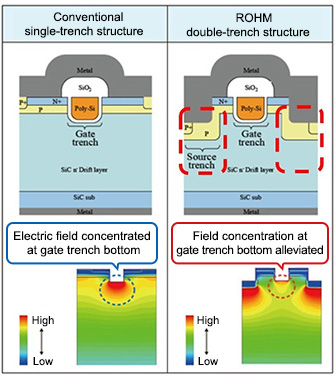

双沟槽型MOSFET(Double-trench MOSFET)

为了解决传统(单)沟槽结构的栅氧化层可靠性挑战,罗姆半导体在其第三代SiC MOSFET中引入了双沟槽结构。

双沟槽结构降低了栅极沟槽底部的电场集中,并最大化了沟道密度以进一步降低导通电阻。通过实施这种设计,罗姆相比其早期的平面型器件,实现了约 50% 的导通电阻降低和 35% 的输入电容降低。

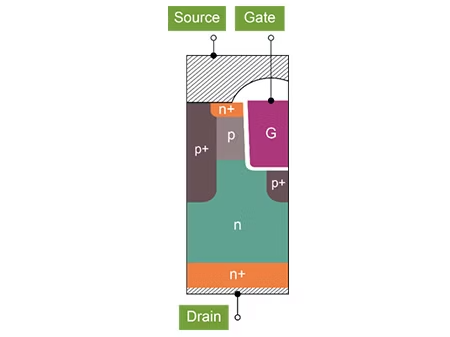

非对称沟槽型MOSFET(Asymmetric trench MOSFET)

英飞凌提出了另一种解决栅氧化层可靠性挑战的方案,在 CoolSiC™系列中引入了非对称沟槽结构,其中沟槽的仅一侧用作沟道。这允许另一侧针对屏蔽进行优化,在开关速度和长期可靠性之间取得平衡。

除了提高栅氧化层可靠性外,该设计还提供了额外的优势,包括减少栅极电荷和降低器件电容,以及减少开关和导通损耗。此外,扩展的 p 型屏蔽区域还充当集成续流体二极管的发射极,改善了反向导通特性并消除了反并联二极管的反向恢复损耗。

英飞凌的 CoolSiC™ MOSFET提供 400 V 至 3300 V 的电压等级,服务于从 AI 服务器电源到高压工业驱动的各种应用。该公司的沟槽技术已通过全球汽车牵引逆变器以及工业系统的广泛部署得到验证。

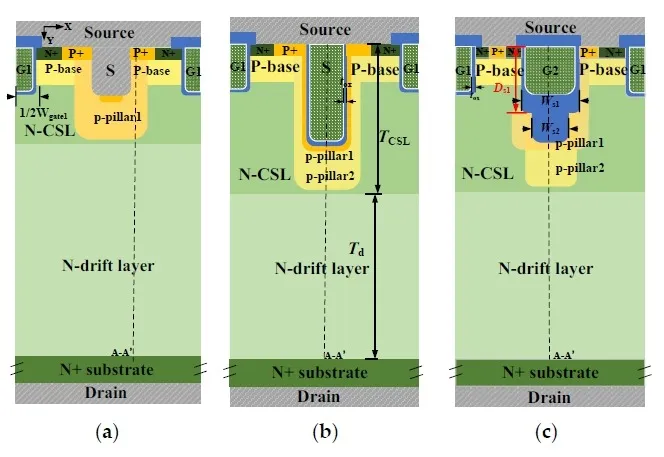

“深” 双沟槽和非对称阶梯沟槽变体

罗姆的第四代SiC MOSFET采用了先进的双沟槽架构,具有更深的 p 屏蔽区域和源极沟槽,以进一步降低栅氧化层电场。这种深双沟槽单元结构(称为 DDT-MOS)与上一代SiC MOSFET中使用的 DT-MOS 双沟槽结构不同。虽然该解决方案显著降低了栅氧化层中的电场,但深源极沟槽占据了单元的更大面积,可能限制了沟道密度的提升。

这一概念的进一步演变是非对称阶梯沟槽MOSFET(AST-MOS)结构。它具有阶梯状沟槽,一侧有额外的电子电流路径,并在底部采用厚氧化层作为耐压区域。

AST-MOS 结构可以看作是罗姆 DT-MOS 和英飞凌科技非对称沟槽 MOSFET(AT-MOS)的混合体。AST-MOS 架构的仿真结果表明,它可以在保持低栅氧化层应力的同时,显著提高击穿电压和导通电阻。

沟槽辅助平面型MOSFET(Trench-assisted planar MOSFET)

沟槽辅助平面(TAP)架构代表了传统平面型和沟槽型设计之间的折衷方案。该拓扑结构现归属于纳微半导体,源自其对 GeneSiC Semiconductor 的收购。该公司现在将此技术纳入其 GeneSiC™产品线。

该解决方案由平面栅极结构组成,在源极区域蚀刻有一个非常浅的沟槽。这种 “源极沟槽” 减小了单元间距(单元之间的距离),而没有垂直栅极沟槽的制造复杂性或氧化层应力风险。

这种混合设计相比平面架构显著改善了导通电阻,同时保持了平面栅极的可制造性和可靠性优势。浅沟槽创建了多步轮廓,有助于增强整个器件的电流扩展,从而在无需全沟槽结构所需的深度蚀刻和复杂工艺的情况下降低了电阻。

V型沟槽MOSFET(V-Groove MOSFET)

三菱电机开发了专有的 V 型沟槽SiC MOSFET,其特征是栅电极嵌入晶圆表面的 V 形凹槽沟槽中。这种 V 型沟槽结构有助于实现高效率,与传统平面型SiC MOSFET相比,降低了沟道电阻并显著减少了功率损耗。

三菱的方法需要专门的蚀刻工艺,还包括将肖特基势垒二极管(SBD)直接集成到MOSFET芯片中,这进一步提高了高压 SiC 功率模块的功率密度和器件性能。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。