手握HBM!韩国AI芯片独角兽,叫板英伟达

全球人工智能推理芯片初创公司的数量堪称庞大 —— 说真的,足足有上百家之多。但在这些公司中,只有一家同时获得了全球三大高带宽内存(HBM)堆叠内存制造商中的两家投资,并得到了其本土国家两大电信巨头的支持。考虑到如今能拿到 HBM 配额的企业,就能打造数据中心人工智能加速器,尽管韩国初创公司 Rebellions AI 进入市场的时间相对较晚,但其入局时机或许恰到好处。

更关键的是,三星和 SK 海力士不仅为 Rebellions 供应 HBM 内存,三星还承担了该公司的代工业务,这些都是 Rebellions 可以借力的核心优势。当前全球市场对矩阵运算的需求已达到狂热状态,而 Rebellions 的目标不仅是在韩国本土销售其 AI 加速器,更要进军全球市场。在 HBM 市场供需极度失衡的当下,这样的产业链支持显得尤为珍贵 ——2025 年底三星与 SK 海力士已将 HBM3E 价格上调 20%,美光 2026 年的 HBM 供应量更是早已售罄,能同时获得两大巨头的资源倾斜,让 Rebellions 在稀缺资源争夺中占据了独特位置。

Rebellions 的后发优势还在于,它亲眼见证了第一批 AI 初创公司的兴衰历程。Groq、Cerebras Systems、SambaNova Systems、Graphcore、Nervana Systems 和 Habana Labs 等先驱企业,要么受制于自身架构设计与资金储备的局限,要么像 Nervana 和 Habana 那样被昔日芯片巨头英特尔收购后逐渐沉寂。Rebellions 首席商务官 Marshall Choy 曾表示,第一代 AI 加速器缺乏灵活性和适应性,未能在市场上取得大规模成功,而作为第二代加速器厂商,他们得以借鉴前人经验,在生态系统成熟之际择机而入,大幅降低了市场风险。

这家 2020 年成立的韩国公司,已通过多轮融资成长为独角兽企业,估值超过 10 亿美元。其投资方包括 KT Corp(原韩国电信)、SK Telecom 等本土电信巨头,而 SK Telecom 与 SK 海力士同属 SK 集团,三星则通过风投部门参与投资,这种深度绑定让 Rebellions 得以稳定获取核心资源。在技术布局上,Rebellions 已从台积电 7 纳米工艺逐步升级至三星 4 纳米工艺,并计划借助三星即将推出的 2 纳米工艺打造混合平台,同时与 Arm、Marvell 等企业达成合作,进一步完善产业链协同。

当前 AI 产业从训练向推理阶段转型,引发了存储需求的革命性增长,一台 AI 服务器对 DRAM 的需求量达到普通服务器的 8 倍,HBM 作为 AI 芯片的 “性能基石”,市场规模预计将从 2025 年的 350 亿美元增长至 2028 年的 1000 亿美元。Rebellions 的 Rebel 系列芯片目前已采用三星 HBM3E 内存,且可兼容 SK 海力士的 HBM 产品,恰好契合了市场对高性能存储的迫切需求。在全球 121 家 AI 处理器研发企业的激烈竞争中,Rebellions 凭借独特的产业链资源、后发的技术沉淀以及对市场需求的精准把握,正试图在英伟达主导的市场中开辟出新的增长空间。

“我常说 —— 第一个老鼠会掉进陷阱,第二个才能吃到奶酪。”Rebellions 首席商务官马歇尔・乔伊(Marshall Choy)在接受《The Next Platform》采访时这样说道。

乔伊在太阳微系统公司(Sun Microsystems)任职十二年,负责技术产品与解决方案工程相关工作。2010 年甲骨文(Oracle)收购太阳微系统后,他继续在甲骨文担任定制化系统领域的相关职务,任期超过八年。这段经历让他亲历了互联网泡沫时期的行业狂热,也见证了互联网技术逐步走向成熟稳定的转型过程。不仅如此,乔伊还是 SambaNova 的创始团队成员,最初担任产品副总裁,后来升任首席客户官,直到一个月前才离职加入 Rebellions。在 SambaNova 任职期间,他曾主导推动 DataScale 集成软硬件系统的产品布局,该系统凭借 1TB 高速内存配置和可重新配置的数据流架构,在大规模 AI 训练任务中展现出显著性能优势。而在甲骨文任职时,他还参与过 Sparc M7 处理器的 SQL 加速器接口开放工作,助力开发者提升编程效率。

“说实话,第一波 AI 加速器缺乏灵活性和适应性,在市场上从未取得过巨大成功。” 乔伊接着说道。这一判断也与行业现实相符 —— 早期 AI 加速器多为特定任务定制,难以适配多样化的 AI 工作负载,且软件栈复杂导致算力利用率偏低。“我们这些第二代玩家,就像是那只第二个老鼠,一直很有耐心。如今生态系统已经成熟,我们正有策略地选择进入各个市场的时机,这大大降低了整体风险。” 乔伊的这番话,既体现了对行业发展规律的深刻洞察,也暗示了 Rebellions 作为后发者的战略考量 —— 借鉴前人经验,依托成熟生态实现精准入局。

Rebellions 于 2020 年 9 月成立时,原本并未打算与英伟达、AMD,以及越来越多来自超大规模数据中心、云服务提供商和模型构建商的自研 AI 加速器正面抗衡。它最初的目标很明确:为高频交易公司打造 AI 推理加速芯片。但世事往往如此,计划总赶不上变化 —— 就像英伟达最初以 3D 图形芯片起家,之后转向为高性能计算(HPC)模拟与建模提供高精度加速,最终才切入更广阔的 AI 市场,并在该领域高速发展了十多年。有些时候,事情的走向虽偏离预期,却可能远比计划中更成功。

这家公司的总部位于被称为 “晨曦之国” 的韩国首都首尔。作为韩国最大的城市,首尔是该国工业与金融的核心枢纽,而韩国本身也是全球重要的经济强国,2025 年预计国内生产总值将达到 1.86 万亿美元,位列全球第十四。(同期美国预计以 30.6 万亿美元位居第一,中国以 19.4 万亿美元紧随其后;欧盟合计约为 21.1 万亿美元,但显然由多个主权国家组成。)值得一提的是,韩国正全力推进 “主权 AI” 国家战略,计划在 2027 年前投入约 5300 亿韩元扶持本土基础大模型研发,这一政策背景也为 Rebellions 的发展提供了有利的本土环境。

Rebellions 由四位联合创始人共同创立,朴成铉(Sung-hyun Park)担任首席执行官。他的教育背景堪称亮眼,本科毕业于韩国科学技术院(KAIST),随后在麻省理工学院(MIT)获得电气工程与计算机科学双硕士学位,辅修金融专业。丰富的学术积累为他的职业生涯奠定了坚实基础 —— 毕业后,朴成铉曾在英特尔担任两年高级研究科学家,之后又先后在三星移动担任工程师、SpaceX 星链部门担任 ASIC 设计师,还在摩根士丹利负责超低延迟股票交易系统设计,这些跨领域的工作经历让他既懂芯片技术,又熟悉金融科技领域的需求,也为 Rebellions 最初的高频交易芯片定位提供了专业支撑。

除了朴成铉,另外三位联合创始人同样具备深厚的行业背景。首席技术官(CTO)吴镇旭本科毕业于首尔国立大学电气工程专业,在韩国科学技术院获得高级学位,曾在 KAIST 担任研究员多年,与微软、德州仪器有过合作,之后加入 IBM 研究院,深耕近似计算、粗粒度可重构阵列和神经网络加速器等核心领域。首席产品官(CPO)金孝恩同样毕业于 KAIST,拥有电气工程学位,曾任职于 Maxwave、三星电子,之后在医疗设备制造商 Lunit 担任首席产品官,积累了丰富的产品经验。第四位联合创始人申成浩毕业于首尔国立大学,是人工智能与算法领域的资深研究员。四位创始人皆出身顶尖学府,且拥有三星、IBM 等行业巨头或科技领军企业的工作经历,形成了技术、产品、算法全方位覆盖的核心团队。

金旭昱(Jinwook Oh)是公司联合创始人兼首席技术官(CTO)。他本科毕业于首尔国立大学电气工程专业,随后在韩国科学技术院(KAIST)取得高级学位。KAIST 与韩国科学技术信息研究院(KISTI)在高性能计算(HPC)及当下的人工智能研究领域保持着紧密合作,这为金旭昱的学术研究提供了有力支撑。在加入 IBM 研究院担任正式职员前,他曾在 KAIST 担任研究员多年,期间与微软、德州仪器展开合作,核心研究方向包括近似计算、粗粒度可重构阵列(CGRA)以及神经网络加速器 —— 这些技术积累成为 Rebellions 芯片架构的重要基础。Rebellions 联合创始人兼首席产品官(CPO)金孝恩(Hyoeun Kim)同样持有 KAIST 的电气工程学位,职业生涯初期曾任职于 Maxwave 和三星电子,之后在医疗设备制造商 Lunit 担任首席产品官,积累了丰富的产品落地经验,最终在 Rebellions 成立之初加入团队。第四位联合创始人申成浩(Sungho Shin)毕业于首尔国立大学,是人工智能与算法领域的资深研究员,为公司的技术研发提供了坚实的算法支持。

融资方面,Rebellions 在 2020 年和 2022 年完成了两轮 A 轮融资,累计融资金额达 6100 万美元。2024 年,公司完成 B 轮融资,由韩国电信(KT Corp,前身为韩国电信)领投,石油巨头沙特阿美的风投部门参与投资。C 轮融资则由 Arm 控股出人意料地牵头,三星风投、和硕风投、韩国开发银行、Korelya Capital、Kindred Ventures 及 Top Tier Capital 等机构共同参与。2024 年 12 月,韩国电信旗下 AI 初创公司 Sapeon Korea 与 Rebellions 完成合并,韩国电信也借此成为 Rebellions 的投资方。值得一提的是,Sapeon Korea 此前已获得 DRAM 及 HBM 内存制造商 SK 海力士的投资,此次合并不仅整合了双方资源,更让 Rebellions 成为韩国首家 AI 芯片独角兽企业(估值超过 10 亿美元),其当前估值大概率已达到 15 亿美元甚至更高。

关键优势在于,韩国电信与 SK 海力士同属韩国第二大企业集团 SK 集团,而三星集团则是韩国最大的企业集团,这两大巨头不仅均对 Rebellions 进行了投资,还为其供应核心的 HBM 内存,三星更是承担了该公司的芯片代工业务,形成了 “投资 + 供应链” 的双重绑定。

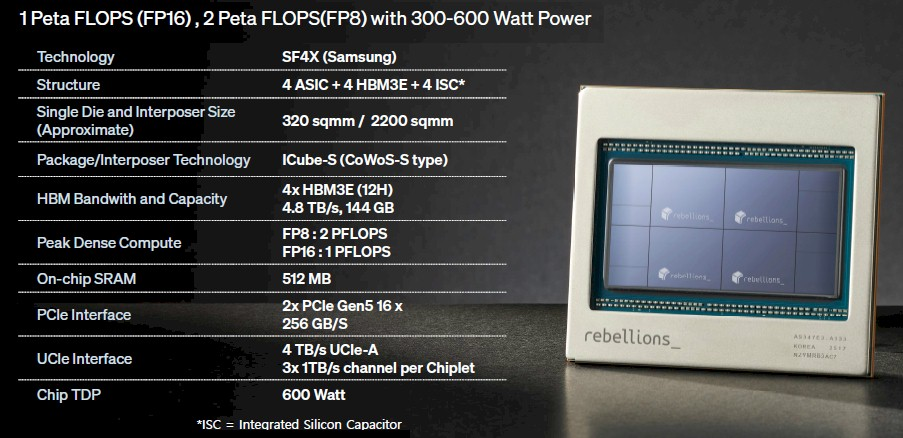

在芯片制造工艺上,Rebellions 的发展路径清晰且持续升级。早期面向高频交易加速的 Ion 芯片采用台积电 7 纳米工艺制造,后续的 Atom AI 推理加速器升级至 5 纳米工艺。而当前备受关注的 Rebel 系列芯片 —— 作为与英伟达、AMD 数据中心级 GPU 加速器直接竞争的核心产品 —— 已采用三星 4 纳米工艺生产。事实上,由于 IBM 的 Power11 处理器并未选择三星 4 纳米工艺,而是坚持使用优化后的 7 纳米工艺,Rebellions 的订单在一定程度上推动了三星 4 纳米工艺的产能爬坡。

近几个月来,Rebellions 的生态布局持续提速。公司已与 Arm 达成合作,加入其 Arm 全面设计(Arm Total Design)生态系统。这一合作将允许基于 Arm Neoverse 架构设计 Arm CPU 的企业,与 Rebellions 的 Atom 或 Rebel AI 加速器进行集成,借助三星即将推出的 2 纳米工艺打造混合计算平台。根据合作规划,该平台集成了 Rebellions 的 REBEL AI 加速器、一致性 NPU 及基于 Neoverse CSS V3 的计算芯粒,预计可为生成式 AI 工作负载(如 Llama3.1 405B 参数大模型)带来 2-3 倍的能效提升。此外,Rebellions 还与 Marvell 展开合作,借助其信号 SerDes(串行器 / 解串行器)、芯片间互连技术及先进封装方案,为客户打造定制化 AI 加速器。这类定制产品尤其适用于亚洲、非洲或中东地区的主权 AI 中心和区域新云服务商,能满足他们对不受美国出口管制限制的 AI 加速器的需求 ——Marvell 的 112G XSR SerDes、PCIe Gen 6 PHY 等技术,可实现高达 240Tbps 的聚合数据传输,有效消除系统级瓶颈。

这些布局最终都指向了第三代 Rebel AI 推理芯片的研发与落地

在混合专家(Mixture of Experts)时代初期,英伟达 GPU、谷歌 TPU 及 AWS Trainium 基本垄断了 AI 训练市场,而推理领域成为企业争夺商业收益的核心战场,Rebellions 将 Rebel 系列及未来芯片的重心放在推理领域,无疑是明智的战略选择。

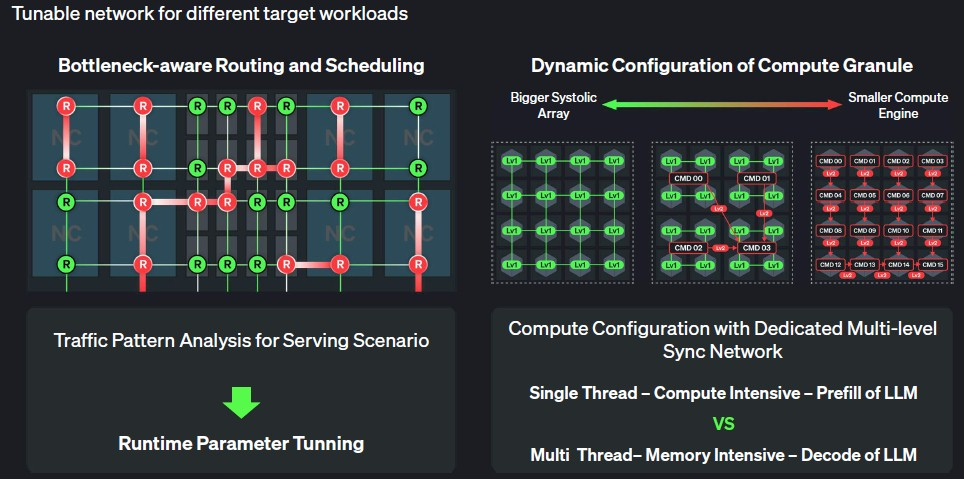

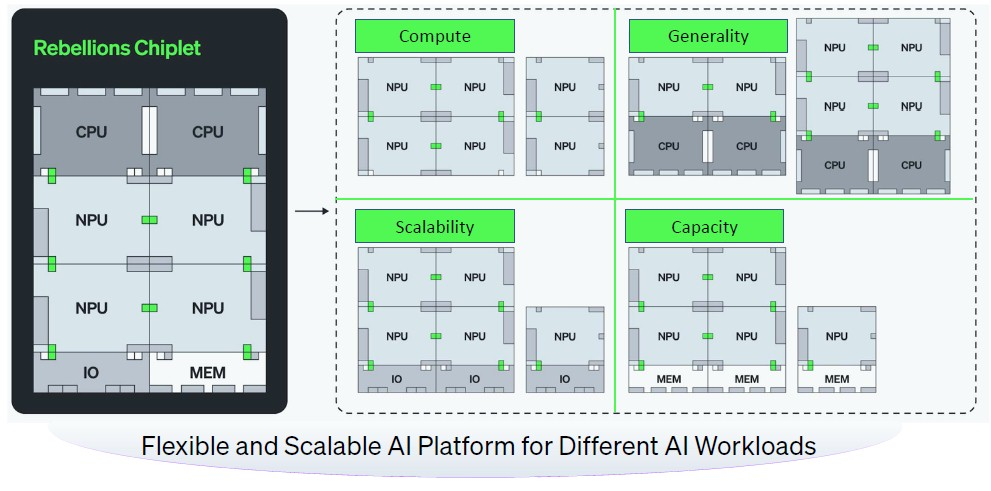

Rebel 芯片的架构借鉴了前代 Atom 芯片的设计精髓,尤其融合了金旭昱在 IBM 期间深耕的粗粒度可重构阵列(CGRA)处理单元设计思路,并与软件定义的片上网络(NoC)相结合。这种架构兼具 ASIC 级的能效与软件级的可编程灵活性,通过 2D 阵列式的字级处理单元,可按周期重新配置计算与互连逻辑,能高效适配多样化的 AI 推理工作负载,完美平衡了性能与灵活性的核心需求。

采用这种架构,Rebel 芯片上任意两个被 Rebellions 称为 “神经核心”(Neural Core)的处理单元之间的路由均可编程,且这种网状互连结构能够跨芯片粒(Chiplet)扩展,从而构建出规模更大的计算与存储复合体。在推理任务运行过程中,芯片内部及多芯片集群间的路由与调度可根据数据流量模式实时调整,这一特性显著提升了系统对动态工作负载的适配能力。

不过,粗粒度可重构阵列(CGRA)架构最具价值的优势或许在于,神经核心上的缓存、加载存储单元、张量单元及向量单元均配备了带有自定义指令集的输入缓冲区(IBUF),使其具备可编程能力。这意味着,在大语言模型(LLM)推理的 “预填充阶段”(Prefill Stage)—— 即提示词被分解为键值对的计算密集型环节,神经核心阵列可被编程为大型脉动阵列(Systolic Array)以高效处理运算;而在 “解码阶段”(Decode Phase)—— 即生成查询对应的 token 响应的内存带宽敏感环节,阵列又可重新编程为更侧重内存带宽优化的架构。正如上图所示,中间还存在多个过渡阶段,架构可根据需求灵活切换。

简而言之,CGRA 架构既保留了现场可编程门阵列(FPGA)的部分可编程特性,又避免了其为实现完全编程灵活性而付出的效率代价,在性能与可编程性之间实现了更优平衡。

与其他 AI 计算引擎类似,Rebel 芯片的神经核心内部集成了多种计算引擎,具体包括:

- 张量单元(Tensor Units):专为矩阵乘法、卷积等 AI 核心运算优化,提供高密度并行计算能力;

- 向量单元(Vector Units):支持高精度标量与向量运算,适用于激活函数、归一化等非张量类计算;

- 加载存储单元(Load-Store Units):负责数据在缓存与内存间的高效传输,减少计算单元等待时间;

- 自定义指令集输入缓冲区(IBUFs):通过专用指令加速数据预处理与后处理,提升整体运算效率。

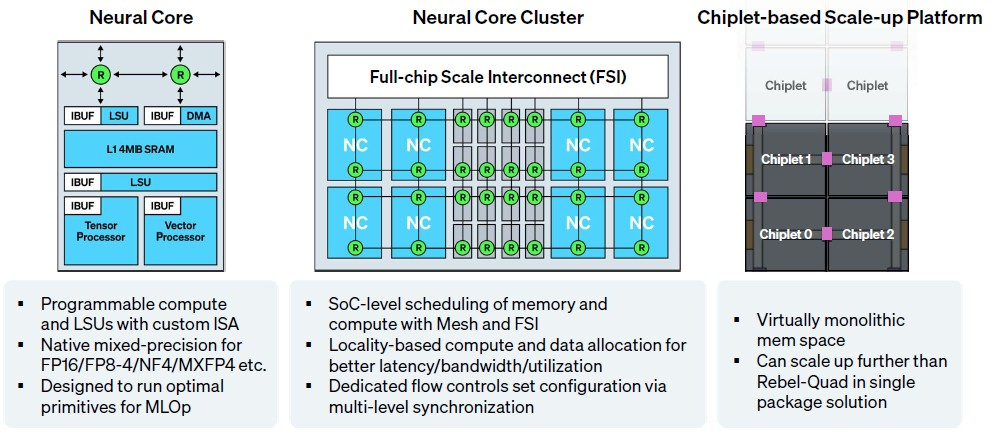

Rebel 神经核心上各计算单元的具体细节目前仍处于保密状态,但已知每个核心配备 4MB 的 L1 SRAM 内存,该内存连接至加载存储单元(Load-Store Unit),而加载存储单元又分别与张量单元(Tensor Unit)和向量单元(Vector Unit)相连。这些运算单元支持 FP16、FP8、FP4、NF4 及 MXFP4 等多种精度,完全满足当前 AI 推理场景的需求。以 Rebel Single 芯片为例,其单个神经核心在 FP16 精度下可提供 16 万亿次 / 秒(TFLOPS)的运算能力,FP8 精度下则达到 32 TFLOPS。由于未公开核心每时钟周期的运算次数,目前无法确定其具体时钟频率,但预计在 2GHz 左右。

为实现芯片级扩展,Rebel 采用模块化设计:8 个神经核心通过 SRAM 模块以网状互连(Mesh Interconnect)方式组成一个计算块(Compute Block),这一架构在 CPU、GPU 及 XPU 等处理器中较为常见。两个这样的计算块被集成在一个名为 “Rebel Single” 的芯片粒(Chiplet)上,形成基础计算单元。

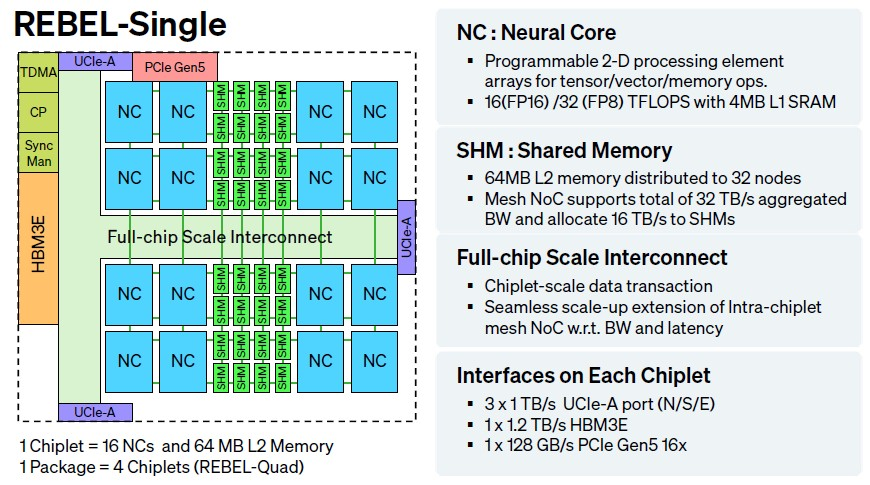

根据架构设计,Rebel Single 芯片粒的核心配置如下:

- 神经核心数量:16 个(2 个计算块 ×8 个核心 / 块)

- 单核心 FP16 算力:16 TFLOPS

- 单核心 FP8 算力:32 TFLOPS

- 单芯片粒 FP16 总算力:256 TFLOPS(16 核心 ×16 TFLOPS / 核心)

- 单芯片粒 FP8 总算力:512 TFLOPS(16 核心 ×32 TFLOPS / 核心)

- L1 SRAM 总容量:64 MB(16 核心 ×4 MB / 核心)

这种模块化设计不仅便于芯片粒级扩展,还能通过跨芯片粒互连构建更大规模的计算集群,以满足不同场景的算力需求。例如,若将多个 Rebel Single 芯片粒集成在同一封装内,可形成算力更强的 “Rebel Multi” 系列产品,进一步提升对大模型推理任务的支持能力。

Rebel Single 芯片配备 1 个 PCI-Express 5.0 x16 接口、3 个 UCI-Express-A 芯片互连接口以及 1 个 HBM3E 内存控制器。目前,Rebel Single 采用三星的 HBM3E 堆叠内存,但从技术兼容性和供应链布局来看,它完全可以支持 SK 海力士的 HBM 内存,且未来极有可能实现这一适配。

在带宽方面,Rebel Single 的各接口表现亮眼:HBM3E 接口带宽高达 1.2TB / 秒,PCI-Express 接口带宽为 128GB / 秒,每个 UCI-Express 接口带宽达 1TB / 秒,3 个接口合计提供 3TB / 秒的芯片间互连能力。芯片内部集成 64 个神经核心,共享 64MB 的 L1 缓存,网状互连架构为缓存分配了 16TB / 秒的带宽,为神经核心分配了同等规模的 16TB / 秒带宽,确保数据在核心与缓存间高效流转。

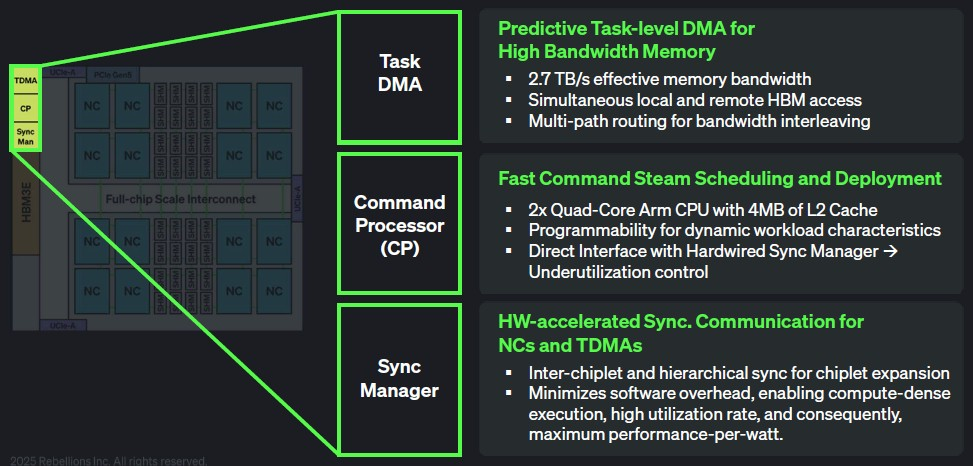

在 Rebel Single 芯片的左上角,有一个独立的电路模块,集成了 TDMA(时分多址)、CP(上下文预取)和 Sync Man(同步管理)功能。这些组件是 AI 推理流程加速的关键设计:

- TDMA(时分多址):通过时间片分配机制,实现多任务对共享资源的有序访问,避免数据冲突,提升并行处理效率;

- CP(上下文预取):提前预测并加载后续推理任务所需的上下文数据,减少核心等待时间,优化推理流水线;

- Sync Man(同步管理):协调多核心、多芯片间的运算同步,确保大规模集群推理任务的一致性和稳定性。

这些设计细节共同构成了 Rebel Single 高效处理 AI 推理任务的核心能力,尤其在大语言模型推理的多阶段流程中,能通过资源动态调度和数据预取优化,平衡计算与内存带宽需求,实现性能最大化。

我们期待对这些模块进行更深入的探究,但目前 Rebellions 仅披露了这些信息。

命令处理器(Command Processor,简称 CP)集成了两个四核 Arm Neoverse CPU 模块,每个模块配备 4MB 的 L2 缓存。其核心任务是辅助上下方的同步管理器(Sync Man)和任务 DMA 控制器,协调并同步多颗 Rebel 芯片间的数据传输,确保计算单元在需要时能及时获取所需数据。从概念上讲,这有点像处理器插槽内 HBM 内存的非统一内存访问(NUMA)控制器,负责优化复杂内存层次结构中的数据流转效率。

这些神经核心集群通过互连组成单插槽内的计算引擎。我们推测,从长远来看,多个插槽可能会基于 UALink 或 ESUN 等扩展网络进行互连,甚至可能根据客户需求采用授权的 NVLink Fusion 互连技术。(目前 Rebellions 对此仍未置评。)

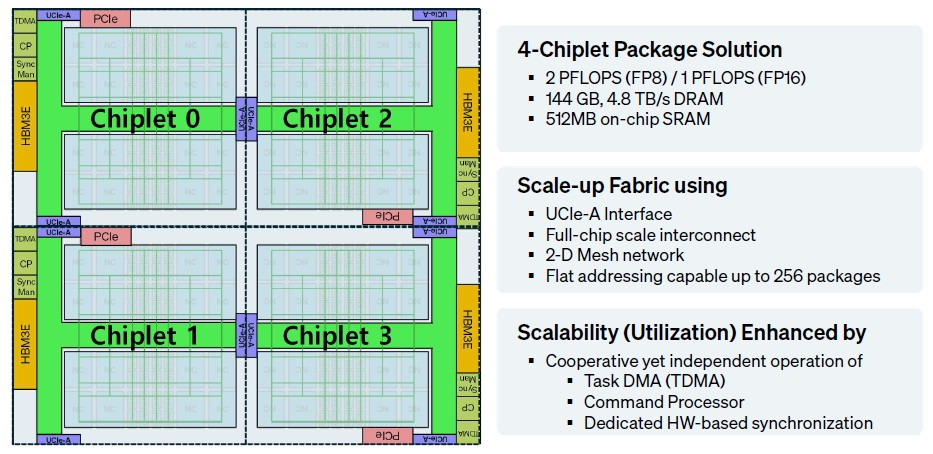

为构建更大规模的计算复合体,四颗 Rebel Single 芯片可通过如下方式连接:

这种连接方式通过芯片间的 UCI-Express-A 接口实现高速互连,形成多芯片模块(MCM)。以四颗 Rebel Single 芯片为例,其集群可提供:

- 总计 256 个神经核心

- FP8 精度下 2048 TFLOPS 的总算力

- 4.8 TB / 秒的 HBM3E 内存带宽

- 3 TB / 秒的芯片间互连带宽

这种模块化扩展能力使 Rebel 系统能够灵活适配从边缘推理到大型数据中心集群的多样化算力需求。

这张示意图展示了由四颗 Rebel Single 芯片组成的集群,显然被称为 Rebel Quad。但正如你所见,你可以在顶部和底部不断堆叠 Rebel Single 芯片对,从而扩展出一个规模极大的、互连的计算与存储平面。理论上,你可以制造一个非常长的 “sled”(一种服务器硬件形态),其逻辑架构相当于晶圆级设计,上面挂载着海量的 HBM 内存,就像圣诞节时售卖的那种巨型士力架巧克力棒。

不过,Rebellions 并不会贸然采取如此激进的设计,除非有客户明确提出需求。但显然,CPU 与 XPU 复合体的互连方式有很多种,Oh 和 Choy 在我们面前暗示了其中的一些可能性:

- 异构集成(Heterogeneous Integration):将 Rebel 芯片与 Arm CPU(如 Neoverse 系列)、IO 芯片等通过先进封装技术(如 CoWoS、InFO 或三星的 H-Cube)集成在同一个封装内,形成一个高度优化的 “系统级芯片”(SoC)。

- 高速互连网络(High-Speed Interconnects):利用 UCIe、CXL、OpenCAPI 或定制的高速串行链路(如 Rebellions 可能开发的 UALink/ESUN),将多个 Rebel Quad 或 Rebel Single 连接起来,构建更大规模的计算集群。

- 内存池化(Memory Pooling):通过 CXL 或类似技术,将多个 Rebel 芯片的 HBM 内存池化,形成一个统一的、可共享的内存空间,提升系统的灵活性和资源利用率。

- 智能网卡(SmartNIC)集成:将 Rebel 芯片的部分功能集成到智能网卡中,实现网络数据的实时 AI 处理和卸载,降低主机 CPU 的负担。

这些可能性表明,Rebellions 不仅在芯片本身的设计上追求创新,也在积极探索未来计算系统的整体架构,以更好地满足 AI 时代多样化的算力需求。

目前,Rebellions 的核心产品是 Rebel Quad—— 一个我们曾亲手拿在手里、但对方坚决不肯让我们带走当镇纸的处理器插槽。

该芯片复合体采用了三星的 ICube-S 中介层和封装技术,其功能与台积电的 CoWoS-S 中介层和封装技术大致相当。该封装包含四组 12 层高的 HBM3E 内存堆叠,总带宽达 4.8TB / 秒,同时配备两条 PCI-Express 5.0 x16 通道,为芯片提供总计 256GB / 秒的内外带宽。(遗憾的是,在四芯片复合体的中间位置,有两个 PCI-Express 控制器被闲置了。)

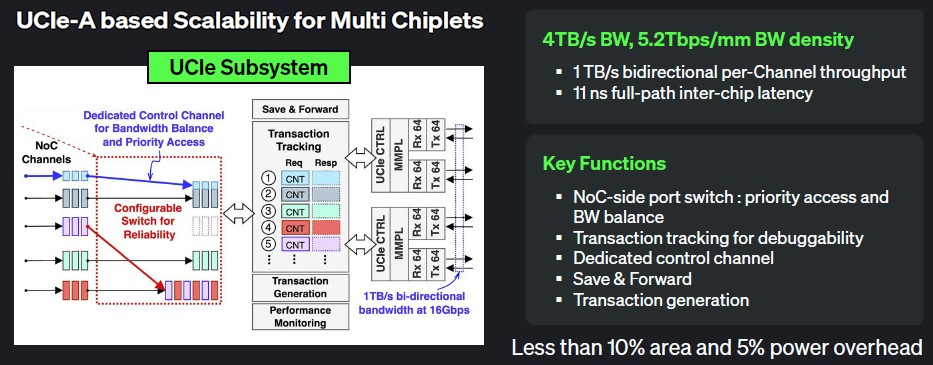

以下是关于 UCI-Express-A 芯片间互连技术的详细信息:

- 技术标准:UCI-Express-A 是一种高速、低延迟的芯片间互连协议,旨在满足 AI 加速器、数据中心处理器等高性能计算芯片的互连需求。

- 传输速率:UCI-Express-A 支持每通道高达 32Gbps 的传输速率,相比传统 PCIe 5.0(32Gbps / 通道)在带宽上相当,但在延迟和功耗方面更具优势。

- 拓扑结构:采用点对点(P2P)或网状(Mesh)拓扑结构,支持多芯片间的灵活互连,便于构建大规模计算集群。

- 功能特性:支持缓存一致性、远程直接内存访问(RDMA)等高级功能,能够有效提升多芯片系统的协同工作效率。

- 应用场景:主要用于连接多个 Rebel Single 芯片,形成 Rebel Quad 或更大规模的计算复合体,以满足高带宽、低延迟的 AI 推理需求。

UCI-Express-A 技术的应用,使得 Rebellions 能够在保持高性能的同时,实现芯片间的高效互连,为构建灵活、可扩展的 AI 计算系统奠定了基础。

Rebellions 的 UCI-Express-A 控制器是从 Alphawave Semi 公司授权的 —— 这家芯片初创公司刚刚被高通以 24 亿美元收购。

这一切带来的最终结果是,Rebel Quad 在 FP16 精度下可提供 1 petaflops 的算力,在 FP8 精度下则达到 2 petaflops。目前尚不清楚在各种 FP4 精度下吞吐量是否会翻倍,或者只是在运算单元的后半部分存在大量闲置的零操作。

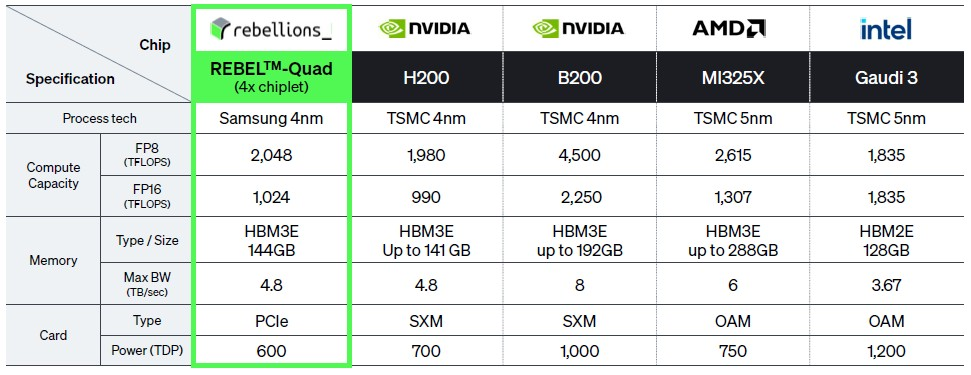

Rebel Quad 插槽的功耗为 600 瓦,与英伟达、AMD 的 GPU 以及英特尔性能大致相当但命运多舛的 Gaudi 3 AI 加速器相比,这一功耗水平相当低。

值得注意的是,Rebel Quad 目前仅提供 PCI-Express 卡形式,暂不支持 OAM 插槽,但客户若有需求,Rebellions 可能会推出适配方案。这一点对液冷服务器尤为关键 —— 此类场景通常需要将芯片平铺在系统主板上,通过顶部铜管覆盖多个计算引擎以提升密度,OAM 插槽的缺失可能限制其在部分高密度部署中的应用。

从原始性能来看,Rebel Quad 与英伟达 H200 相当,FP16 和 FP8 算力分别高出 3.4%,且每瓦性能提升 20.7%,能效优势显著。英伟达 B200 的性能是 Rebel Quad 的 2.2 倍,但需消耗 1.7 倍带宽和功耗,属于合理的性能功耗比。AMD MI325X 的每瓦性能与 Rebel Quad 接近,浮点吞吐量高出 28%,但需额外 25% 的内存带宽和功耗支持。

不过,实际性能可能因架构差异而有所不同,尤其是在真实推理场景下,Rebellions 的 CGRA 架构在动态任务适配方面可能更具优势。Rebellions 尚未公布价格,但考虑到当前 HBM 和张量计算资源供不应求的市场环境,其定价策略可能更注重价值而非低价竞争。

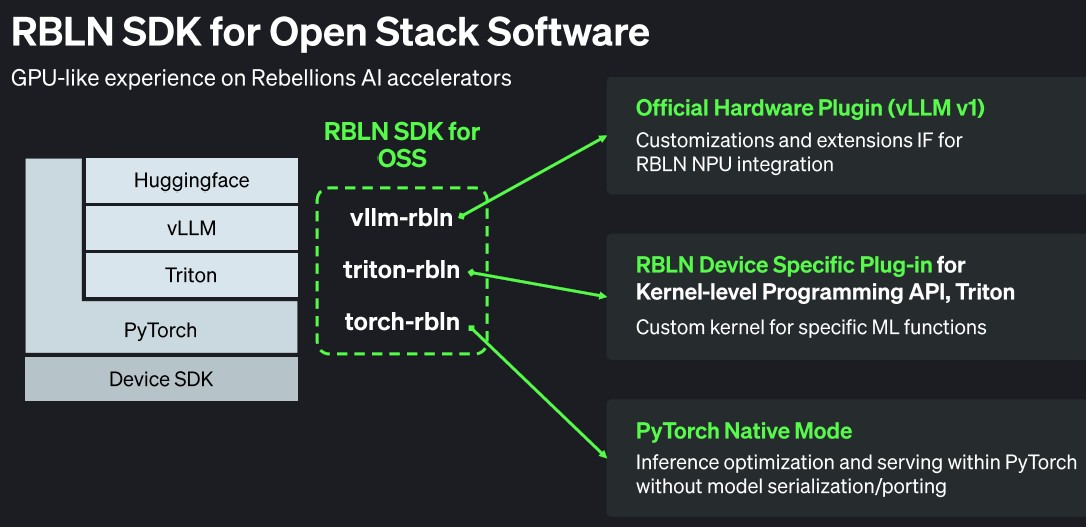

Rebel Single 已于 2024 年 11 月流片,Rebel Quad 目前正向部分客户提供样品用于概念验证设计。在硬件布局完成后,Rebellions 正着力构建软件生态:其软件栈基于开源技术,通过 PyTorch 原生实现结合 Triton 推理引擎,利用 vLLM 库管理推理过程中的键值缓存。此外,Rebellions 还开发了类似英伟达 NCCL 的集体通信库 RBLN CCL,基于开源 MPI 库构建,旨在优化多芯片集群间的数据传输效率。

这些软硬件协同设计,加上 Rebellions 与三星、SK 海力士在 HBM 供应上的紧密合作,使其在当前 AI 加速器市场中具备独特的差异化竞争优势。

Rebellions 还开发了名为 Raise 的推理服务层,功能类似于英伟达的 Dynamo 推理栈。Raise 已集成到 Ray 分布式推理框架中,该框架运行在红帽的 OpenShift Kubernetes 容器平台及其基于红帽企业 Linux 的容器变体之上 —— 后者源自多年前红帽对 CoreOS 的收购,当时 The Next Platform 才刚刚起步。

这一软件生态的构建,使得 Rebellions 的硬件能够更好地融入现代数据中心的基础设施,为客户提供从芯片到服务的完整解决方案。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。