UCIe 3.0增加DSP支持

小芯片的普及及其多样化的用途促使成立了一个联盟来制定和监督标准,因此最新的更新针对特定的新兴市场领域也就不足为奇了。

日前,UCIe联盟发布了其 UCIe 开放标准 3.0 版本,旨在实现同一封装内芯片之间的高速、可互操作连接。UCIe 联盟主席 Debendra Das Sharma 表示,新版本的标准与早期版本完全向后兼容。

3.0 版的更新旨在满足生态系统需求和联盟 140 家成员公司的要求,以及高性能计算 (HPC) 和人工智能 (AI) 系统的需求。

两年前,该联盟发布了 UCIe 1.1 以满足汽车合规性要求,而 2.0 版本则增加了对 3D 小芯片的支持。Das Sharma 表示,2.0 版本的发布还解决了测试和调试方面的问题,包括凸点间距减小引起的问题以及固件升级。“这本身并不是一个互连问题,但却是一个需要解决的问题,”他说道。

Das Sharma 表示,UCIe 3.0 的目标是将带宽翻倍。“我们基本上是通过平面互连将数据速率翻倍,这是因为人们无法获得足够的带宽。” 通过进一步缩小凸块来实现更高的带宽。“如果凸块缩小,那么我的带宽实际上可以翻两番,”他说道,“但这需要在工艺方面做出更多改进。”

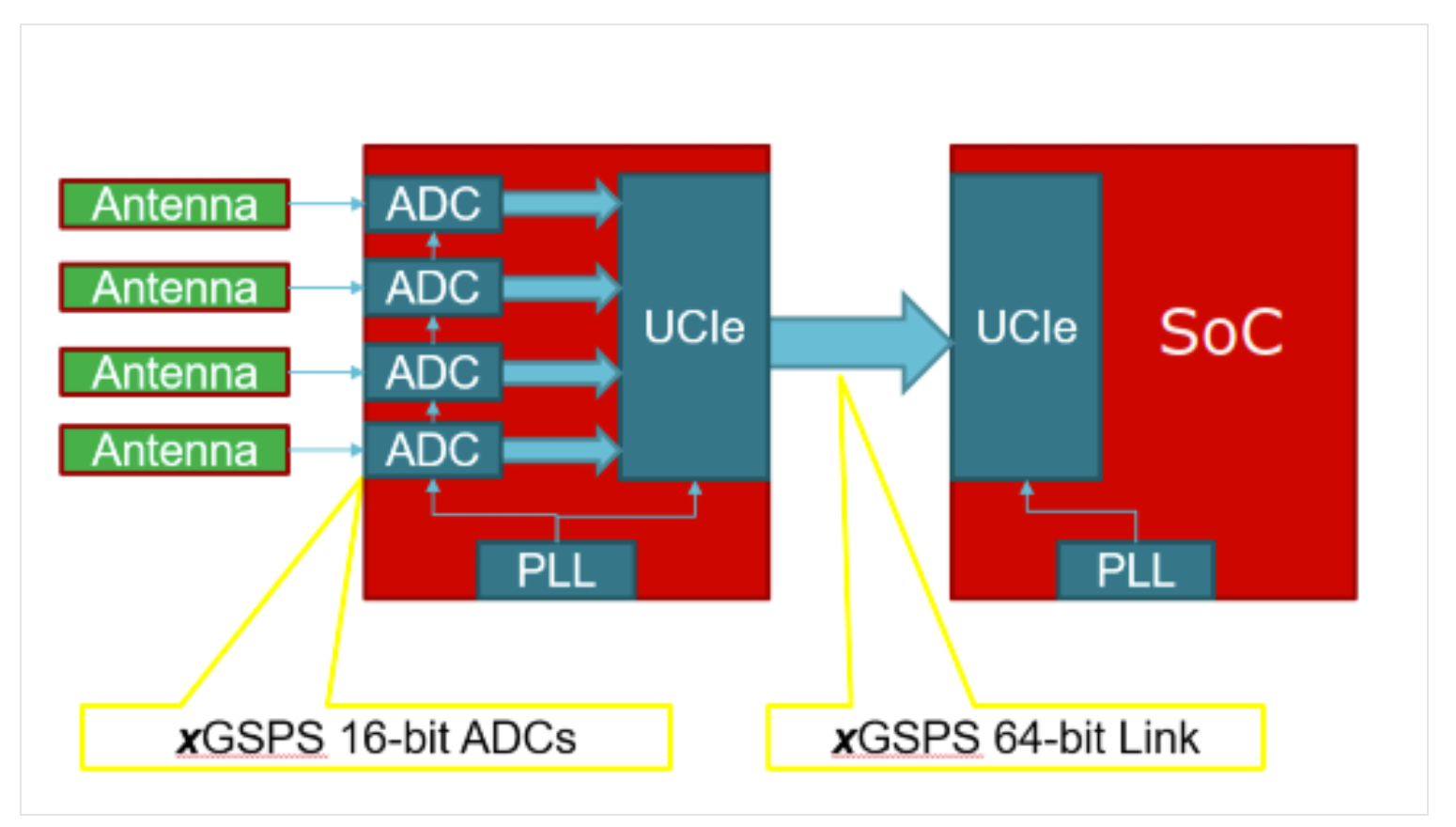

数据转换器之间的高速数据传输协议现在可以映射到 UCIe Raw 操作模式,这使得 DSP 供应商无需单独的 PLL 即可使用 UCIe 标准。来源:UCIe 联盟

与半导体标准的情况一样,UCIe 3.0旨在实现这些带宽目标,同时保持低功耗,这对于 AI 密集型数据中心来说是一个关键关注点。

本次更新中特别提到了一个领域,旨在帮助 DSP 供应商支持新的应用,例如 SoC 和 DSP 芯片之间的连接。Das Sharma 表示,UCIe 联盟中活跃的主要 DSP 供应商对更好地利用芯片感兴趣,并需要解决敏感模拟电路的功率转换挑战。“对此类支持的请求非常迫切。”

数据转换器之间的高速数据传输协议现在可以映射到 UCIe Raw 工作模式,这使得 DSP 供应商无需单独的 PLL 即可使用 UCIe 标准,同时避免在敏感的模拟电路中引入额外的频率噪声。这是通过利用现有的 Raw 模式,增强内部 RDI/FDI 接口,并重用 UCIe Retimer 编码来发送周期性同步标记和奇偶校验来实现的。

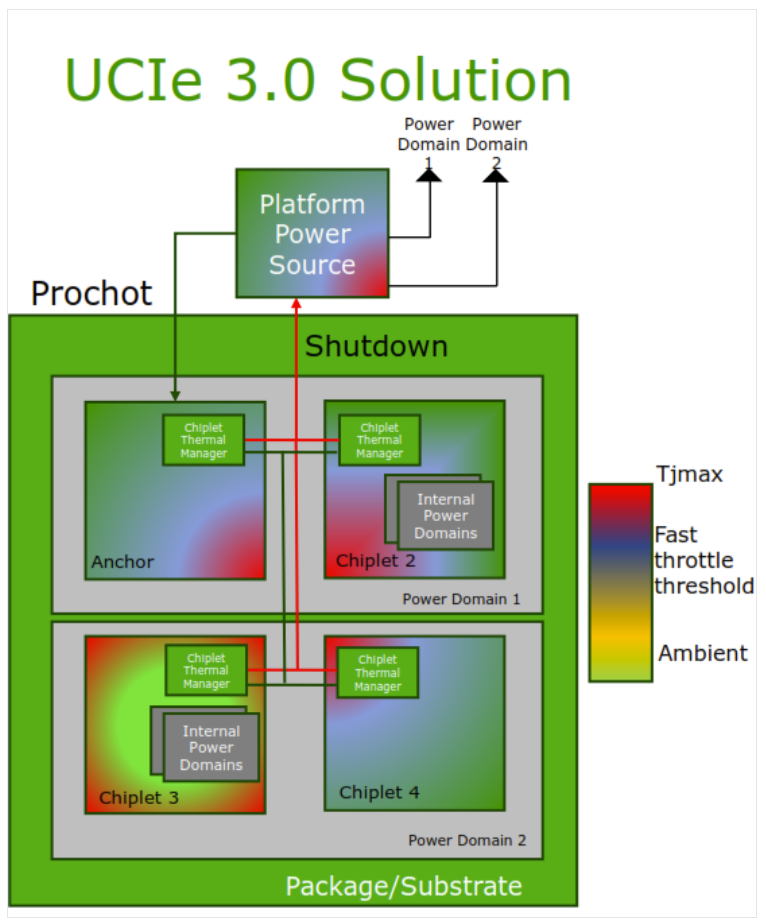

UCIe 3.0 新增了快速节流/关断功能,使所有参与的芯片都能按照预先协商好的水平和规定的速率进行节流。来源:UCIe 联盟

Das Sharma 表示,通过满足 DSP 供应商的需求,UCIe 解决了新的细分市场问题,包括无线基础设施、软件定义无线电和雷达系统。

他表示,随着小芯片在其他应用(包括笔记本电脑和手持设备)中的应用,预计新的领域将继续对 UCIe 变得重要。

另外,更新的重点是更高的带宽密度,UCIe-S 为 48 GT/s,UCIe-A 为 64 GT/s,旨在将数据速率提高一倍,以满足在海岸线限制下的 HPC 和 AI 应用中使用的 SoC 对更高线性带宽密度的持续需求。

Das Sharma 表示,带宽密度的提升与降低功耗的努力相辅相成。“我们一直在寻找可管理的低功耗方法。” UCIe 3.0 的变化使得 UCIe-S/UCIe-A 的黑白密度线性提升至 1.65 倍/2 倍,同时保持了相似的功耗效率。

UCIe 3.0 中的节能是通过运行时重新校准和 L2 优化实现的,通过重复使用初始化状态并减少边带上的空闲功率,可以在运行期间实现节能的链路调整。

可管理性基础设施增强包括早期固件下载、边带优先级数据包、扩展边带范围、开漏引脚和快速节流/关断,确保所有参与的芯片以定义的速率节流到预先协商的水平。

Das Sharma 表示,展望未来,UCIe 联盟将致力于在封装级别建立开放的芯片生态系统和无处不在的互连,以解决服务器 AI、边缘 AI、网络、汽车和消费者存储领域的各种用例。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。