SoC设计自动化大突破,从概念到FPGA验证仅需数分钟

无晶圆厂半导体初创企业 InCore Semiconductors宣布,其基于专有SoC(系统级芯片)生成器平台开发的测试芯片成功通过硅验证。InCore称,这一突破为自动化芯片设计勾勒出大胆的未来图景——完全定制化的SoC从概念到FPGA验证的周期可从数月缩短至几分钟。

这一创新的核心是InCore的SoC生成器,这是一个功能强大的自动化平台,旨在从根本上简化并加速SoC开发。传统上,即便是基于FPGA的定制SoC原型开发,也需耗时数月,原因在于IP集成、互连设计和软件就绪度之间存在复杂的相互作用。而 InCore的平台将这一周期压缩至短短几分钟——自动生成互连结构、集成IP,并即时生成在FPGA上启动软件所需的全部配套文件。

“InCore的愿景是消除早期SoC设计中的阻碍,”公司联合创始人兼首席技术官尼尔・加拉表示,“借助我们的SoC生成器,架构师能在10分钟内从概念推进至FPGA验证。这对所有硅产品开发者而言都是颠覆性变革。它不仅支持快速且高可信度的原型开发,还能简化设计空间的探索——如果我想尝试多种SoC架构方案,只需用10种不同配置运行这个工具,喝杯咖啡的功夫,就能在实际FPGA硬件上看到运行结果,还能同步获得初步的PPA(功耗、性能、面积)评估区间。”

“这不仅是一个工具,更代表着芯片设计方式的变革,”公司联合创始人兼首席执行官G・S・马杜苏丹称,“通过将设计与验证周期从数月缩短至几分钟,我们为更快的创新、更低的成本以及更广泛的参与者打开了大门。”

他谈及当前芯片设计的现状及降低行业门槛的必要性时指出:“随着摩尔定律逐渐停滞,专用计算时代已然来临,芯片设计正经历剧烈变革。历史上,英伟达、迈威尔、博通等半导体巨头通过定制ASIC(专用集成电路)建立了自己的帝国。但这种专业化伴随着高昂代价:数亿美元投入、数千名工程师团队、长达数年的开发周期——只有少数大公司能负担得起。如今,我们敢于打破这种高成本的现状,让小型团队也能拥有此前无法触及的SoC设计‘超能力’。尤其是随着RISC-V架构的渗透率不断提升,即便是大型老牌企业也希望快速将产品组合迁移至RISC-V,而我们的平台旨在成为他们的核心赋能者。”

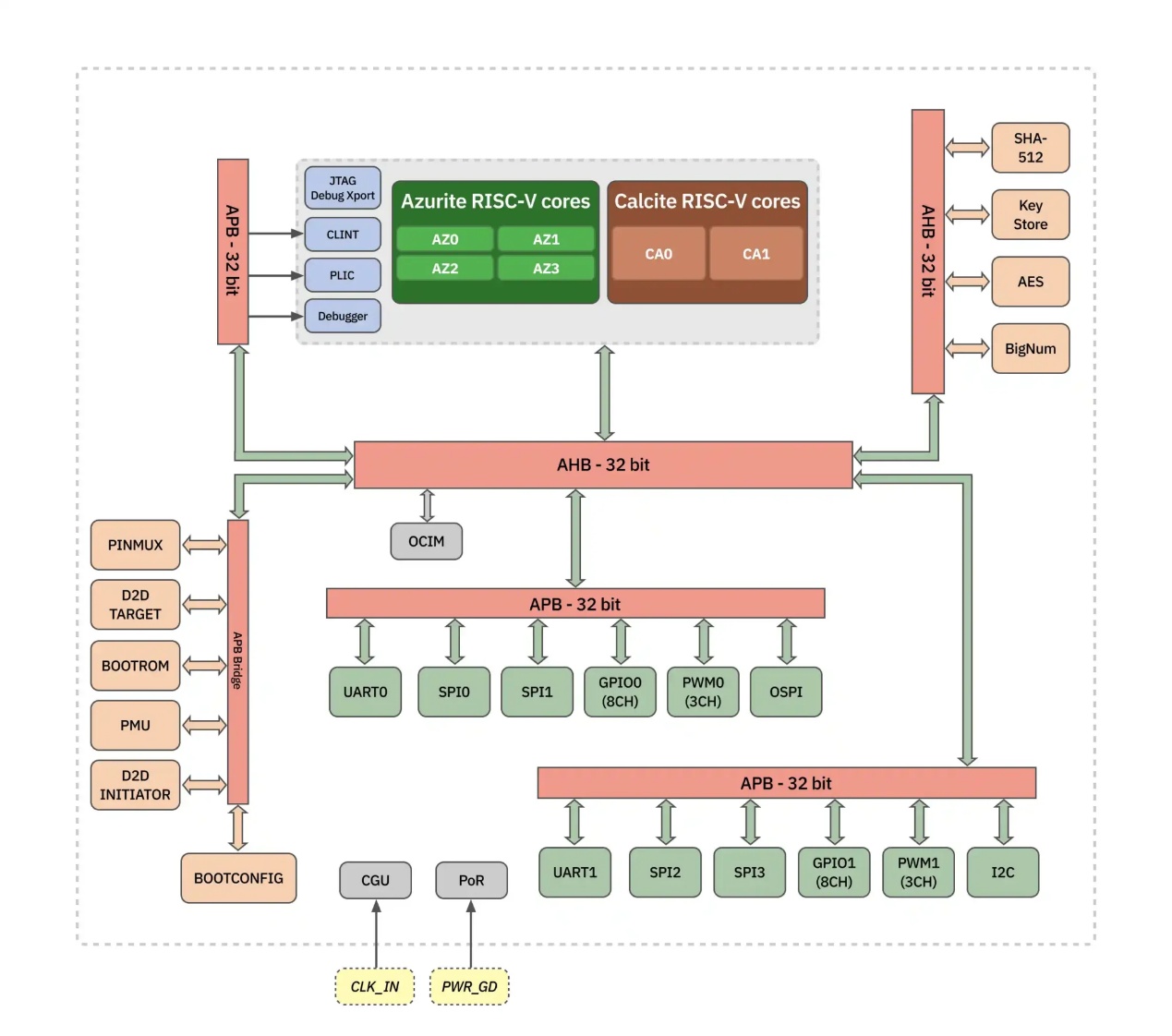

InCore近期完成流片的测试芯片(基于台积电40nm工艺节点),印证了该平台已具备硅级就绪能力。这款芯片由SoC生成器平台设计,集成了6个异构RISC-V内核、一个定制的内部NoC以及多个外设IP。平台还同步生成了芯片的软件配套文件和文档。目前,该芯片已成功启动,并能运行实时操作系统(RTOS),验证了其功能与架构的可靠性。

以这款测试芯片的设计流程为案例:传统方法需要3-4名SoC工程师耗时2-3个月才能从概念推进至RTL(寄存器传输级)冻结阶段。而借助SoC生成器平台,一名SoC设计师仅用几分钟就完成了SoC RTL的初稿设计。经过多轮迭代优化配置后,RTL冻结在2-3天内即可完成。此外,软件、验证和物理设计等下游团队能够提前介入工作,显著缩短了整体芯片设计周期。

在与新兴的生成式AI芯片设计工具对比时,尼尔・加拉表示:“我们的SoC生成器追求的是确定性精度,而非基于模式匹配的猜测。”他将这种可靠性与当前生成式AI的不确定性进行对比:“芯片设计涉及数十亿种可能场景,错误不仅代价高昂,更可能是灾难性的。这需要绝对的准确性,而非概率性的‘幻觉输出’。因此,我们的目标是为用户提供类生成式AI的SoC设计能力,同时通过确定性约束确保硬件无缺陷。”

InCore计划将SoC生成器平台作为独立解决方案,向全球无晶圆厂半导体企业和SoC团队提供。

InCore Semiconductor成立于2018年,正在印度生产第五代RISC/RISC-V处理器内核。 RISC(精简指令集计算机)是一种微处理器架构,它使用较少数量的计算机指令类型,从而使系统能够以更高的速度运行。

InCore由Arjun Menon、Gautam Doshi、GS Madhusudan和Neel Gala创立,总部位于印度理工学院马德拉斯研究园。2023年,这家初创公司从Peak XV Partners筹集了300万美元。

该初创公司旨在使印度成为RISC-V解决方案领域的强国。其处理器内核为高性能应用级处理器、面积/功耗优化的嵌入式处理器等提供支持。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。