imec首席执行官:业界应该朝着“可重构”AI芯片发展

人工智能算法的开发速度比当前开发专用 ASIC 来解决人工智能数据流和计算中的特定瓶颈的策略要快。IMEC 年度技术论坛于周二在比利时安特卫普开幕,并于周三继续举行。

专用集成电路可能需要一到两年的时间来开发,并需要六个月的时间在晶圆厂制造。

据报道,范登霍夫表示:“搁浅资产存在巨大的固有风险,因为当人工智能硬件最终准备就绪时,快速发展的人工智能软件社区可能已经发生了变化。”范登霍夫提出的是一个三维、可编程的人工智能计算处理元素阵列。

英伟达凭借其为人工智能提供多处理GPU,发展成为最大的半导体公司。这些GPU足够通用,能够处理不断开发的多种类型的人工智能算法。此外,其CUDA并行计算平台和编程模型也使其免受竞争。

但即便如此,Nvidia 的 GPU 并非特定算法最节能的解决方案。因此,超大规模计算平台和其他公司一直在寻求开发 ASIC 加速器,以应对数据中心的特定工作负载。

范登霍夫表示,虽然较大的公司可能能够承担得起这一点,但对于大多数公司来说,这是有风险且不经济的。

随着人工智能的前沿从大模型(LLM)转向多模式代理人工智能(Agentic AI),算法变革的步伐甚至可能正在加快。IMEC 首席执行官预计将提出,未来的人工智能芯片将多种人工智能计算方式组合成一个块状处理单元——即所谓的超级单元(Supercell)。这样,可编程片上网络将能够链接和编程资源,以动态地满足算法需求。

该方法将利用三维堆叠和其他先进的封装方法。让人联想到现场可编程门阵列 (FPGA),但其抽象程度比原始的门级查找表 (LUT) 更高。超级单元(阵列中的构建块)很可能由丰富的内存计算处理组成,以支持广泛的 AI 需求。

虽然这种方法看似合理,但需要注意的是,如果AI算法持续偏离组件超级单元支持的某些计算方式,那么“AI版FPGA”将包含冗余硅片,并成为一种昂贵但可能仍然节能高效的解决方案。平衡性能、功耗和面积(PPA)仍然是芯片设计人员面临的挑战,而FPGA传统上因其上市时间优势而被选中,但单位成本更高。

英特尔代工厂、台积电和三星代工厂正在争相提供完整 3D-IC 的所有基础组件,这些组件将在未来几年内以最小的功耗实现性能的大幅提升。

3D-IC 已出现在代工厂的内部路线图上十多年,但直到两年前 ChatGPT 的推出以及随后 AI 数据中心的建设,完整的芯片堆叠才真正获得发展势头。从那时起,人们的重点就一直放在功耗和性能的大幅提升上,而实现这一目标的最佳方法是分解 SoC,并行处理大量计算元件,并减少信号在不同处理元件和存储器之间来回传输时遇到的距离、电阻和电容。

这些目标显而易见,但实现这些目标所需的一些技术仍在开发中。正因如此,所有晶圆代工厂都宣布计划在未来几年内分别投入约 1000 亿美元,实现 3D-IC 的量产。

许多问题亟待解决,其中大多数问题需要提前解决,并在硅片上进行验证,才能最终实现。从技术或经济角度来看,仅仅依靠平面微缩的功耗、性能和面积/成本优势已远远不够。

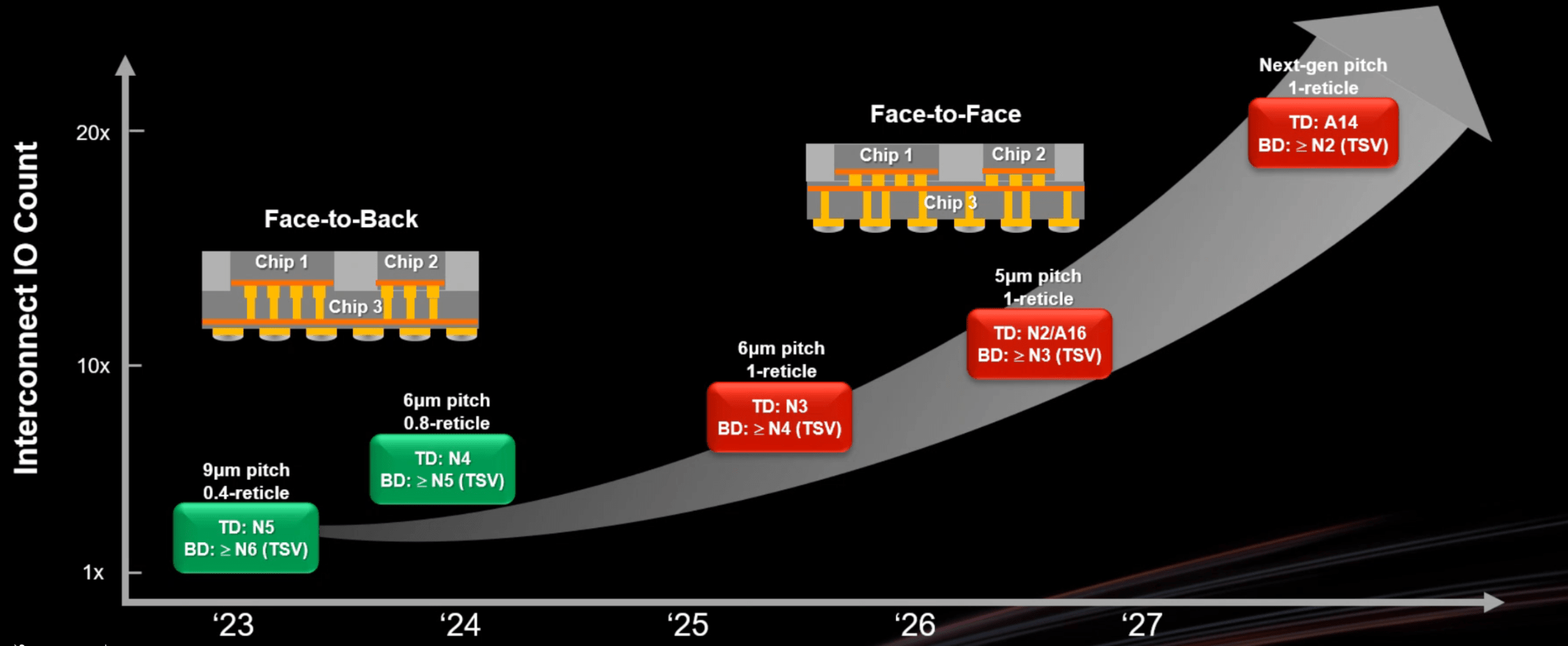

台积电3D IC路线图展示了不同的集成策略

台积电业务发展和全球销售高级副总裁张凯文表示:“晶体管技术和先进的封装集成必须齐头并进,才能为我们的客户提供完整的产品级解决方案。3D 结构技术组合对我们来说非常重要。”

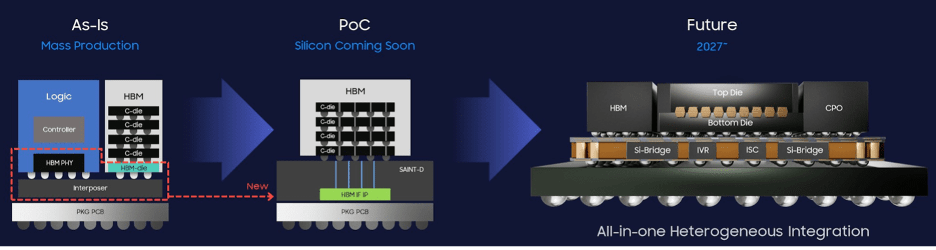

三星 3D IC 路线图

在去年春季的一次演示中,三星代工业务开发副总裁 Taejoong Song 展示了一份路线图,该路线图以逻辑叠层技术 (LCOE) 为特色,将 2 纳米 (SF2) 芯片与 4 纳米 (SF4X) 芯片组合在一起,两者均安装在另一个基板上。这本质上是一个 2.5D 封装(有时也称为 3.5D)上的 3D-IC。Song 表示,该代工厂将从 2027 年开始在 SF2P 上堆叠 SF1.4。

3D IC 的初期应用将集中在 AI 数据中心内部,但一旦工艺完善、问题得到解决,这种方法将能够更广泛地应用,并实现更有针对性的组件组合。所有应用是否都需要完整的 3D-IC,还是只需要部分核心技术,仍有待确定。尽管如此,堆叠芯片中正在解决的技术问题将具有广泛的应用前景。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。