投资2亿美元,日月光押宝FOPLP

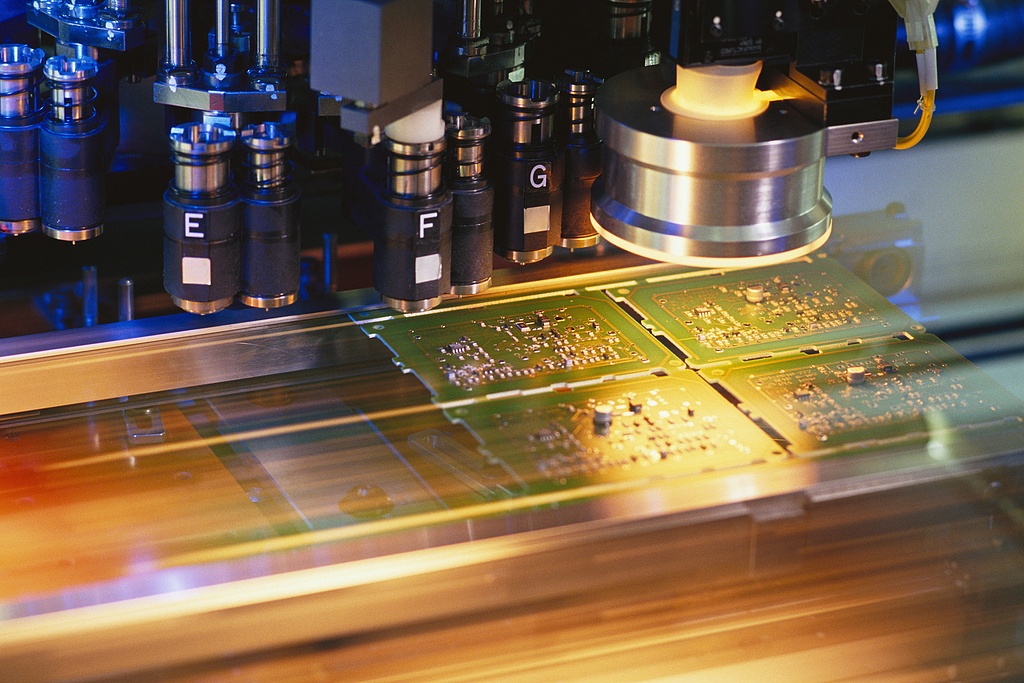

2月18日,半导体封测大厂日月光投控马来西亚槟城五厂正式启用,扩增当地封测产能。

据介绍,日月光马来西亚厂区由目前100万平方英尺将扩大至约340万平方英尺。未来,日月光将持续投入资源与人力资本,以获取更多市占率,并拓展服务范围与深度。而且,此次扩厂将带动更大的招聘需求及培训发展,未来几年内预计将新增1,500名员工,为全球半导体产业培养更多高阶技术人才,加速产业升级。

而在此次开工典礼上,日月光投控营运长吴田玉还宣布,决定在中国台湾高雄厂区投入2亿美元(约新台币66亿元)设立面板级扇出型封装(FOPLP)量产线,预计第二季设备进厂,第三季开始试量产。

吴田玉还透露,日月光高雄厂区最新的面板级扇出型封装尺寸为600mm×600mm,目前已有众多客户。

目前台积电、群创、力成等科技大厂均投入面板级扇出型封装领域,日月光投控这次开出的尺寸规格,比外界盛传台积电开发的尺寸还大。随着日月光投控积极开发面板级扇出型封装,确立相关技术未来将成为主流,台积电、群创、力成等厂商也将同步抓住商机。

随着高性能计算和人工智能领域的需求增长,CoWoS技术因其高集成度和优异性能而受到越来越多的关注。CoWoS(Chip-on-Wafer-on-Substrate)技术是台积电为了克服摩尔定律即将面临的物理限制,于2013年开发出的一种先进封装技术。但由于成本较高,初期只有少量采用Xilinx。

随着时间的推移,CoWoS技术得到了进一步的发展与应用。2016年,台积电发布了第二代CoWoS方案,硅中介层尺寸大约是1.5倍reticle limit,并包含4个HBM2,总容量为16GB。2019年,台积电开发的第四代CoWoS装有一个逻辑芯片和6个HBM2,总容量为48GB(384Gbit),是第三代容量的3倍。

2021年,台积电发布第五代CoWoS技术,其晶体管数量是第三代的20倍。CoWoS-S5通过将插层尺寸扩大到3倍reticle limit(2500 mm²),可在单个插层上集成3个或更多逻辑芯片组和8个HBM。

目前AI芯片封装以台积电的CoWoS技术为主。台积电正在扩大CoWoS封装产能以应对市场需求。

不过,台积电CoWoS的产能增长,预计仍然无法满足市场的需求,于是AI芯片厂商积极探索替代方案。

扇出型板级封装(FOPLP)是将芯片再分布在矩形载板上,然后采用扇出(Fan-out)工艺进行封装。业界看好,FOPLP有望接棒台积电的CoWoS,成为未来AI芯片封装新主流。

这主要是因为现行采圆形的基板可置放的芯片随着芯片愈来愈大,无法达到有限切割需求,若改由面板级封装的方形基板进行芯片封装,数量会比采用圆形基板多数倍,达到更高的利用率,并大幅降低成本。

随着AI应用快速发展,对芯片性能、体积、散热、成本及封装等要求更加严苛,伴随5G、AIoT、车用芯片等应用同步大开,对高性能、高功率半导体需求大增,面板级扇出型封装不仅可提升芯片性能,更能显著降低成本,并解决散热、信号串接等问题,成为大厂积极投入的领域。

吴田玉强调,AI芯片昂贵,封装时置放的颗粒越多,相对风险也增高,若非客户强力支持,日月光不可能跨出设立量产线的大步。

日月光十年前即投入FOPLP研发,初期采用300mm×300mm规格,在试作达到不错效果后,尺寸推进至600mm×600mm,并于去年开出设备采购单,相关机台预定第二季及第三季装机,今年底试产,若试产顺利,预定明年送样客户验证后,即可量产出货。

吴田玉认为,若600mm×600mm面板级扇出型封装良率如预期顺利,相信会有更多的客户和产品导入,届时可望成为业界主流规格。随着客户导入面板级扇出型封装,可解决现有12寸晶圆尺寸已不敷使用的问题,日月光透过与客户合作,将机柜(Rack)平面化、变成“大平台”,除整合内存与GPU在同块板子上,板子间也透过共同封装光学元件(CPO)连接,提升传输速度及整体运算效率,且为确保电源供应稳定,也将电源供应封装在板子底部。

据悉,日月光原先已有高阶封装FoCoS设计构架,其中扇出型FOCoS-Bridge封装技术,整合多颗特殊应用芯片(ASIC)和高频宽内存(HBM),锁定定制化AI芯片先进封装市场。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。