先进封装将推动下一代HPC性能

设计节能系统以满足高性能计算(HPC)的高带宽需求,这涉及硅技术的主要趋势:提高晶体管密度、增强内存容量以及加强逻辑 IC 与内存之间的互连。对更多晶体管的需求促使芯片设计突破掩模版限制(已超出先进封装的范围),不过,其他两个趋势可通过先进的半导体封装技术有效应对。

增强内存容量可通过集成高带宽片上内存和增加 I/O 数量来达成,而这两者都能借助先进的封装技术实现。同样,改善逻辑 IC 和内存 IC 之间的互连对系统性能至关重要,先进的封装为此提供了必要的框架。

成本管理依旧是该领域的关键重点。小芯片设计的出现为处理器开发提供了一种模块化方法,能让供应商优化成本和性能。通过对不同组件采用不同的工艺节点,小芯片设计可最大程度减少对不太重要部件使用昂贵先进节点的依赖,进而降低总体成本。此外,对更多 I/O 的需求推动着将 I/O 芯片与处理单元集成在同一模块中。利用 2.5D 或 3D 先进半导体封装技术(这种技术可实现亚微米布线),该方法能够增加 I/O 数量、增大内存容量并提升系统性能。

先进半导体封装趋势

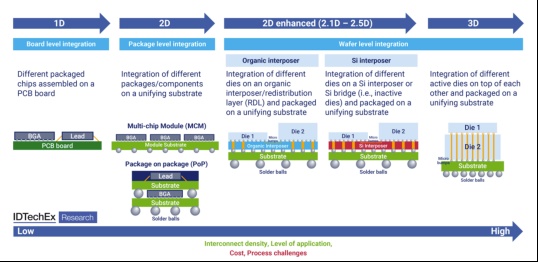

半导体封装技术已从基本的 1D PCB 级发展到晶圆级的先进 3D 混合键合,实现了超细互连间距和超过 1000 GB/s 的带宽,同时还具有很高的能效。这一发展由四个关键因素推动:通过创新设计提高能效、通过增加 I/O 点和减少互连长度来提高性能、通过平衡用于高性能计算的更大封装和紧凑的 3D 集成来优化面积、通过不断寻找更实惠的材料和提高制造效率来降低成本。

图 1. 半导体封装的演进路线图。

图 1. 半导体封装的演进路线图。

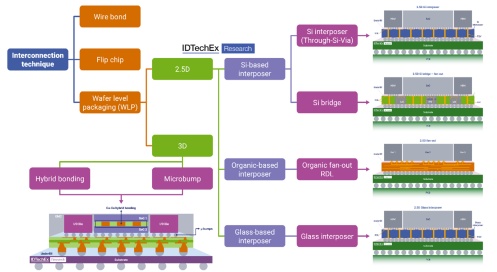

图 2. 先进半导体封装技术概览,按不同的互连技术分类。

图 2. 先进半导体封装技术概览,按不同的互连技术分类。

2.5D封装

2.5D 封装涉及使用中介层在同一封装上水平连接不同的芯片(裸片)。中介层主要有三种类型:

硅 (Si) 中介层:这些中介层目前是 HPC 的主流,因为它们能够支持最精细的布线功能,从而实现高性能集成。然而,材料成本高、制造标准高以及封装面积有限带来了挑战。为了缓解这些问题,局部 Si 桥(仅在必要时策略性地使用 Si)正在获得关注。这种方法有助于克服面积限制,尤其是超过 4 倍或 5 倍光罩限制时。

有机中介层:使用扇出型模塑料的有机中介层被认为是一种经济高效的硅替代品。不仅材料和制造工艺更便宜,而且扩大到面板级封装(例如 FOPLP - 扇出型面板级封装)可以进一步降低成本。传统硅晶圆的利用率不到 85%,而面板的利用率超过 95%。600×600 毫米面板的有效面积是 300 毫米硅晶圆的 5 倍以上,可将总成本降低 60% 以上。面积利用率的提高可提高生产能力、增强 AI 芯片的设计灵活性并大幅降低成本。此外,这些材料可以采用更低的介电常数进行设计,从而减少电阻电容 (RC) 延迟并提高性能,尽管实现硅基中介层可能实现的精细互连特性仍然具有挑战性。

玻璃中介层:玻璃因其可调的热膨胀系数 (CTE)、高尺寸稳定性和光滑的表面而成为一种有吸引力的选择,非常适合精细布线。此外,玻璃可以实现面板级封装,从而大大降低成本。尽管有这些优势,但玻璃中介层的生态系统仍在成熟,目前大规模生产能力有限。然而,随着这些挑战得到解决,玻璃有望在半导体封装中发挥更重要的作用。

3D封装

3D 封装涉及垂直堆叠芯片,从而实现更紧凑、更高效的设计。这里的两项关键技术是:

微凸块技术:这种历史悠久的方法使用热压键合 (TCB) 在堆叠芯片之间创建垂直互连。虽然微凸块技术可扩展,但将凸块间距(凸块之间的距离)减小到个位数微米会带来诸多挑战,例如金属间化合物 (IMC) 的形成增加,这会降低导电性和机械性能。焊球桥接的风险也会增加,可能导致芯片故障。

混合键合:这种先进技术通过将介电材料与嵌入式金属(通常是铜)相结合来创建永久连接(Cu-Cu 键合)。混合键合可实现非常精细的间距尺寸,通常低于 10 微米,从而带来显著的优势,例如更高的 I/O 数量、更高的带宽、更好的功率效率和更低的寄生效应。然而,制造的复杂性和成本仍然是重大挑战。台积电是 3D 混合键合技术的领先供应商,该技术目前已用于多款高端服务器产品,包括部分 AMD Instinct 和 EPYC 型号。

用于2.5D和3D封装的介电材料

在 2.5D 半导体封装中,实现高带宽取决于再分布层 (RDL),其中包括线/空间尺寸、通孔尺寸和焊盘布局等关键特性。SiO2 等传统无机电介质可以实现精细的线/空间特性,但受到高介电常数 (Dk=3.9) 的阻碍,并且由于与硅制造技术相关而成本高昂。这会损害高速通信并增加成本。

有机电介质材料因其较低的介电常数和成本效益而被探索作为可行的替代品。然而,选择合适的有机电介质需要平衡几个因素,正如 IDTechEx 的“先进半导体封装材料和加工 2024-2034 ”报告中所强调的那样。关键参数包括介电常数 (Dk)、损耗角正切 (Df)、热膨胀系数 (CTE)、断裂伸长率、杨氏模量和吸湿性。理想情况下,材料应具有较低的 Dk 和 Df、与硅和铜兼容的 CTE、较高的伸长率以实现柔韧性,以及中等的杨氏模量以实现稳定性。然而,选择材料通常需要权衡利弊;例如,具有低 Dk 的聚合物可能具有较高的 CTE,这会影响器件的可靠性和封装设计。平衡这些参数对于优化半导体封装中的材料性能至关重要。

在 3D 半导体封装中,混合键合现在采用无机电介质,如 SiO2 或 SiCN,它们在精细图案化制造方面面临困难,需要先进的前端制造技术。有机电介质与 2.5D 封装中使用的类似,具有介电常数较低、RC 延迟减少和缺陷容忍度提高等优点。它们还可能允许后端制造技术,从而降低生产壁垒,使更多行业参与者参与其中,增强生态系统并降低成本。然而,由于高键合温度和与化学机械平面化 (CMP) 的兼容性等挑战,有机电介质在 3D 混合键合中的使用仍在开发中。高温会影响敏感材料,铜和聚合物之间的模量差异使键合过程复杂化。尽管存在这些挑战,但它仍然是增强 3D 封装技术的有希望的研究领域。

共封装光学元件

光互连对于下一代高端数据中心至关重要,因为它们可以克服限制数据传输速度的 I/O 瓶颈。光互连使用光而不是电来利用光子,光子不受阻力并且可以以最小的损耗长距离传播。与传统的电气方法相比,这可以实现更高的带宽和更快的芯片和芯片间数据传输。随着数据中心对速度和效率的要求不断提高,光互连促进了快速、高容量通信,解决了关键的性能和可扩展性挑战,并确保硬件能够有效满足不断增长的数据需求。

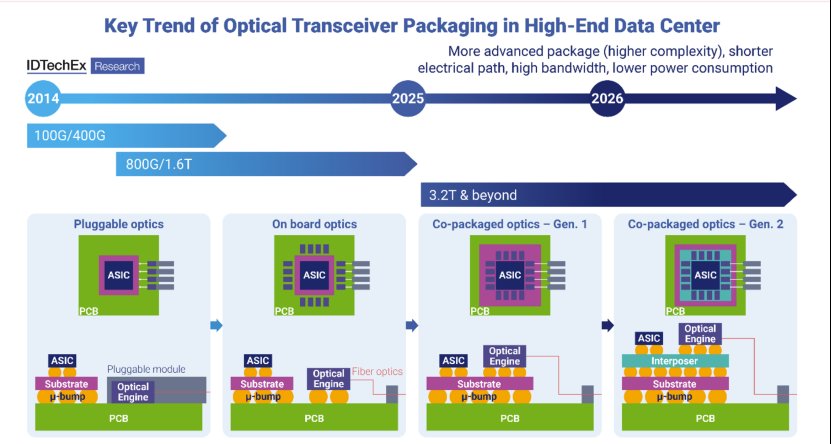

图3.高端数据中心光模块的关键趋势。

图3.高端数据中心光模块的关键趋势。

从可插拔光收发器(高端数据中心的现有光收发器技术)向共封装光模块 (CPO) 的过渡,是由解决信号完整性和集成密度限制的需求所驱动的。由于数据速率和连接器密度的增加,可插拔光模块面临着高功耗和信号完整性问题。相比之下,CPO 将光模块直接集成到交换机 ASIC 上,缩短了电气距离并提高了信号完整性。这种方法提高了性能,支持更高速的数据传输,并克服了传统可插拔模块的限制,优化了每条通道的通信数据速率。

先进的半导体封装是共封装光学器件 (CPO) 的关键推动因素。例如,集成光子 IC (PIC) 和电子 IC (EIC) 的方式会影响带宽密度和封装寄生效应。3D 单片集成提供最小的寄生效应,但使用较旧的 CMOS 节点进行 EIC,从而影响性能和能耗。2D 集成提供最低的成本,但存在显著的寄生效应和降低的带宽,因此不适合 CPO。2.5D 集成在可控的寄生效应和成本之间实现了平衡,但效率低于 3D 混合解决方案。3D 混合集成使用有源中介层中的 TSV、Cu-Cu 键合等技术,最大限度地减少了寄生效应并提供最佳性能,尽管它面临热管理挑战。

发展前景

由于技术、经济和市场因素的相互作用,先进半导体封装正在经历显著增长。随着硅片规模接近极限,先进封装为提高芯片性能提供了一种可行的替代方案,特别是对于需要更高计算能力和带宽的高性能计算 (HPC) 应用(如人工智能和数据中心)。该技术促进了不同芯片的异构集成,满足了对更高带宽和更高功率效率的需求,同时还在芯片制造成本不断上升的情况下提供了经济高效的解决方案。此外,5G、人工智能、汽车和工业应用的激增,加上全球竞争和供应链动态,正在加速这些封装技术的进步和采用。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。