如何优化芯片堆叠的晶圆边缘工艺

使用短而直接的晶圆到晶圆键合垂直堆叠芯片可以将信号延迟降低到可忽略不计的水平,从而实现更小、更薄的封装,具有更快的内存 / 处理器速度和更低的功耗。

晶圆堆叠和芯片到晶圆混合键合的实施竞争已经开始,目前这被视为堆叠逻辑和内存、3D NAND 以及 HBM 中可能的多层 DRAM 堆叠的关键所在。垂直堆叠使芯片制造商能够将互连间距从铜微凸块中的 35µm 跃升至 10µm 及以下。

但垂直化是有代价的,这让芯片制造商不得不努力寻找减少晶圆边缘缺陷的方法。这些缺陷可能会脱落,进而成为影响产品良率的因素。而将晶圆粘合在一起需要非常平坦、无缺陷的 300 毫米晶圆。为了在整个晶圆加工过程中以及在融合和混合键合过程中更好地控制晶圆边缘缺陷,工程师们正在对新工艺和现有工艺进行微调。这些工艺包括晶圆边缘的湿法和干法蚀刻、化学机械抛光 (CMP)、边缘沉积和边缘修整步骤等一系列技术。

性能和能效的提升令人惊叹。Brewer Science 全球业务运营执行董事 Alex Smith 表示:“先进封装通过芯片堆叠开始实现更高的处理速度和能力,使内存与 CPU 和 GPU 更紧密地结合在一起。我们获取信息并返回处理信息的线路越短,计算速度就越快。”

其他人也同意这一观点。“您会发现数据移动仍占芯片本身成本的很大一部分,因此您需要数十或数百个内存访问周期,而获取所需值则可能需要两到四个周期,”Synopsys 产品管理高级总监 Kenneth Larsen 说道。 “如果我们能够将内存更靠近处理器,系统性能将得到大幅提升。而且,在堆栈中上下发送信号可以大大节省能耗,而不需要长时间将信号从芯片发送到外部内存并返回。”

工艺也正在根据先进封装的特定需求进行设计。例如,Lam Research 及其合作伙伴 CEA-Leti 优化了去年推出的先进封装应用的边缘沉积工艺。在晶圆减薄之前,键合晶圆上的边缘沉积可提供加固。

Lam Research 产品营销总监 Ian Latchford 表示:“这些结构需要材料来填充边缘的间隙,故而沉积的薄膜充当了支撑层。否则,器件晶圆在 CMP 过程中可能会于边缘处破裂,原因在于边缘处的去除速度更快。由此,晶圆上存在一个被称为 CMP 滚降的斜率,这会致使晶圆之间形成间隙,直至间隙为零。如果没有边缘沉积,晶圆减薄过程中可能会在晶圆边缘处发生破裂,从而严重影响产量。”

使用基于 AI 的先进工艺控制 (APC) 软件,工程师可以改进整个晶圆以及堆叠内晶圆之间的均匀性分析。“我们提供从中心到边缘的等离子体约束、从中心到边缘的薄膜均匀性、从中心到边缘的光刻工艺等的实时 APC,”Tignis 解决方案工程总监 Boyd Finlay 说道。 “我们还分析堆叠在一起并按时间、配方、工具、腔室或技术进行切片的多个晶圆。”

为混合键合准备的晶圆必须满足关键工艺规格才能实现高良率的混合键合,例如极高的平整度(中心到边缘不均匀度 <1nm)、键合晶圆上无颗粒、晶圆 / 晶圆或芯片 / 晶圆对准异常、芯片放置精度 <200nm 等等。边缘缺陷包括颗粒、碎裂、划痕、薄膜剥落、晶圆处理过程中的损坏。

CMP 挑战

IBM 于 20 世纪 80 年代末首次开发 CMP,用于引入铜镶嵌互连,CMP 极大地推动了晶圆平坦化以及将更多功能集成到更薄的设备中。晶圆平整度、受控边缘卷边和减少颗粒是 CMP 的主要目标。现在,除了 CMP 用于平坦化浅沟槽隔离、BEOL 互连中的电介质和铜之外,晶圆研磨和 CMP 正在得到优化,以在键合后大幅减薄 300 毫米硅晶圆背面。

器件晶圆的质量还取决于起始硅的质量。“多年来,晶圆边缘的加工一直是个难题,”TECHCET 市场研究和分析高级总监 Mike Walden 说道。“由于边缘之外没有邻近材料,所以会发生中断或突变,从而改变这些区域的物理特性。在抛光裸硅晶圆时,我们已采取措施进行补偿,例如使用挡圈。在这种 CMP 中,有一个挡圈支撑抛光槽中的晶圆。晶圆边缘仅与挡圈的极小部分相接触,裸硅晶圆边缘基本上被塑造成三个部分 —— 一个锥形、一个更钝的边缘,接着是另一个锥形。事实证明,与更圆的边缘相比,这种形状更利于提高 CMP 性能。”

产量对所有晶圆工艺都至关重要。“如果 CMP 速度过快,就会产生不均匀性,而且更有可能造成机械损坏,”Walden 说道。“因此,在最大化去除率与控制均匀性和缺陷率之间,需要进行非常微妙的权衡。”

CMP 工具供应商(例如 Applied Materials、Ebara Technologies 和 Axus Technology)与垫片和浆料供应商一起,针对每种应用(例如 BEOL 互连中的铜 CMP)优化晶圆和晶圆间均匀性。Tignis 的 Finlay 表示:“他们同时为目标工艺应用设计整个耗材套件(浆料、垫片、修整盘、P-CMP 清洁剂)。这些工具还针对修整臂扫掠速率、垫片寿命和垫片直径进行控制。”

化学和机械工程考虑了工具、垫片和浆料的组合。“CMP 垫片有多种特性需要控制,包括刚度或硬度。颗粒大小、分布和成分非常重要,因为它们在一定程度上决定了整个晶圆以及晶圆之间的去除率,”Walden 说。他补充说,表面图案工程和优化的垫片调节技术也被使用,垫片表面的实时感应和反馈也是如此,因此用户可以随时调整 CMP 工艺并进行修正。

CMP 和湿 / 干蚀刻工艺均经过优化,可使用专用工具去除晶圆边缘缺陷。

干法和湿法蚀刻

“斜面蚀刻已投入生产约 15 年,可通过去除任何不良材料(会损坏晶圆或从斜面移动到晶圆中心的颗粒缺陷)来提高产量,”Lam 的 Latchford 说道。“客户在整个生产线上实施斜面蚀刻,因为在工艺流程中的某些点上会堆积东西。”

蚀刻机经过优化,可去除晶圆边缘上任何类型的薄膜,无论是电介质、金属还是有机物。在斜面反应离子蚀刻 (RIE) 过程中,晶圆由顶板和底板固定,所以只有晶圆边缘、斜面以及晶圆背面边缘处于暴露状态。

蚀刻工艺的使用方式各不相同,具体取决于客户和具体流程。“有些客户会等到积聚了一层薄膜后再去除,直到硅表面恢复原状。其他时候,他们只是试图去除一层薄膜,比如用于 NAND 流程深度蚀刻的厚碳硬掩模,”Latchford 解释道。这种碳掩模还具有导电性,会导致 RIE 腔内产生电弧,因此最好将其去除。

“如果工艺流程中有 500 或 800 个步骤,通常会在某些地方堆积薄膜或使表面变得粗糙,” 他说。“因此,我们利用斜面蚀刻来解决一些潜在的污染问题。”

尽管湿式和干式清洗工艺各有优势,但设备制造商通常会选择其中一种进行大批量生产。“20 年来,人们一直在尝试去除边缘缺陷和斜面,”ACM Research 首席技术专家 Sally Ann Henry 说道。“显然,随着技术节点的不断降低,这已成为一个更大的问题,因为人们希望从晶圆边缘获得更多优质芯片。我们目前的边缘排除量为 2 毫米,而客户更喜欢 1 毫米,因此晶圆边缘的缺陷变得越来越重要。”

为了在最终研磨 / 减薄步骤期间和之后成功处理这些薄晶圆,首先将器件晶圆键合到符合半导体行业原始晶圆标准的玻璃晶圆或硅载体晶圆上。在键合步骤之前,这些晶圆将经过至少一个 CMP 处理步骤、相关的 CMP 后、键合前清洁步骤以及键合过程本身。如果这些步骤未达到关键质量,键合晶圆的边缘甚至整个配合表面可能会出现空隙。

“例如,如果你有一层氮氧化硅薄膜,由于斜面的附着力较弱,薄膜可能会剥落,” 亨利说。“你可以用 DHF 去除它。如果你有氮化钛 (TiN) 之类的东西,热应力会导致薄膜剥落,所以可以用 SC1 去除它,你也可以用类似的方法去除背面的聚合物。等离子蚀刻薄膜后,背面边缘会出现聚合物。CMP 后也会出现薄膜剥落。你需要去除它,以防止剥落的部分重新沉积在晶圆正面,造成缺陷并损坏设备。”

专用清洗剂提供边缘蚀刻。“我们有一个斜面清洗系统,将晶圆置于中心,然后使用非常少量的化学品清洗晶圆的边缘,使用传统化学品清洗外部 1.05 毫米 - SC1、稀 HF、SPM(硫酸 - 过氧化氢混合物),或者可能是 HF 和硝酸的混合物,具体取决于您要去除的薄膜,” 她说。“在晶圆旋转时,通过小喷嘴施加化学品,在晶圆顶部使用氮气来高精度地控制斜面边缘清洁。”

由于薄晶圆的处理和加工是一项巨大的挑战,大多数芯片制造商在加工过程中使用晶圆与玻璃晶圆的临时粘合来提供支撑。“大多数人都将其粘合到玻璃晶圆上。在我们的大多数工具中,我们会同时清洁晶圆的正面和背面,” 亨利说。“因此,对于一些非常薄的应用,特别是当你将晶圆减薄到可能只有 200µm 厚时,客户会使用 Tyco 环来固定晶圆,因为弯曲是最大的问题。”

目前最先进的技术是使用玻璃晶圆载体来粘合 / 剥离薄晶圆,其中有机粘合剂将晶圆粘合到玻璃上,然后使用激光或紫外线剥离工艺将其剥离。这些工艺与使用集体处理的晶圆到晶圆或芯片到晶圆处理兼容。有多种粘合剂可用于高温或低温的晶圆处理过程。

“Brewer Science 的专业领域是临时键合和解键合的薄晶圆处理工艺,”Smith 说道。“有趣的是,10 年前,如果你解键合了晶圆并清洗干净,然后用显微镜检查,如果没有残留物,你就会说,‘好吧,没问题。’但现在,随着混合键合的出现,清洁度要求确实加快了。因为如果有任何颗粒,都可能影响产量,”Smith 说道。

干法沉积

NAND 设备是 Lam 开发斜面沉积技术的第一个关键应用(见图 1 和图 2)。“斜面沉积系统沉积一层保护性二氧化硅层,我们首先开始研究 3D NAND 设备的边缘沉积,”Latchford 说。“现在它已经扩展到其他应用。最有趣的用途之一是实现 3D 封装的键合晶圆应用。沉积可以在正面、斜面和 / 或背面的前几毫米上进行,厚度从几百埃到几微米不等。”

Lam 的系统是借鉴其斜面蚀刻工具和其他沉积系统的经验而建立的。“我们采用了斜面蚀刻系统中建立的许多关键 IP 和功能,例如一流的精密晶圆定心和等离子整形技术,并将其应用于去年推出的边缘沉积系统。”

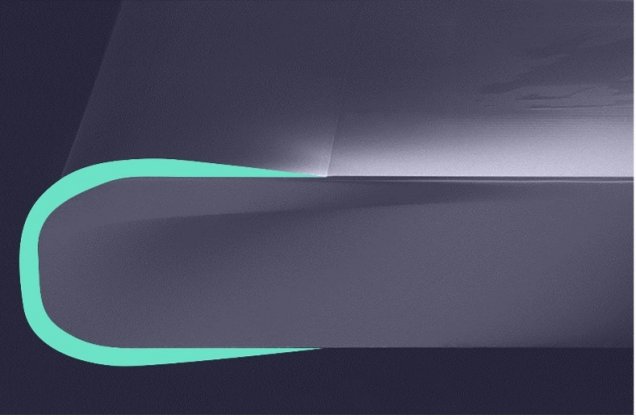

图 1:Coronus DX 工艺在斜面区域沉积一层二氧化硅薄膜。来源:Lam Research

图 1:Coronus DX 工艺在斜面区域沉积一层二氧化硅薄膜。来源:Lam Research

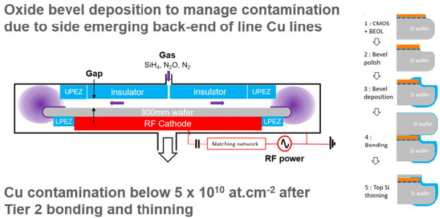

目前正在研发的另一项新应用涉及沉积薄氮化硅膜以控制铜污染。对于现有应用,Lam 工程师预计每一步的产量将提高 0.2% 至 0.5%。

图 2:斜面沉积系统示意图(左),以及斜面沉积、键合和减薄流程的工艺流程。来源:CEA-Leti

图 2:斜面沉积系统示意图(左),以及斜面沉积、键合和减薄流程的工艺流程。来源:CEA-Leti

晶圆减薄和边缘修整

先进设备的基础硅晶圆减薄会产生很大的应力。TECHCET 半导体封装和材料高级市场分析师 Shaun Bowers 表示:“当我们减薄时,底层硅会变得越来越薄,因此多种热应力和机械应力会以变形的形式显现出来。例如,对于 NAND 和先进逻辑设备,剩下的硅很少。其余的都是金属堆栈,所有这些层都会增加应力。”

要了解去除了多少硅,必须考虑原始晶圆。“对于 300 毫米硅晶圆,从 775 微米开始,完成所有设备处理后,将其减薄至 35 至 50 微米,”Walden 说。“特别是当你开始考虑内存计算这个概念时,你将逻辑堆叠在高性能、高带宽内存之上,你会拥有完全不同的设备,两者之间存在完全不同的力和压力。”

边缘修整工艺是一种湿法工艺,可以去除晶圆外层 1 至 1.5 毫米,可以在键合前或键合步骤中进行。EV Group 业务开发总监 Thomas Uhrmann 表示:“对此有不同的看法。但假设您正在进行熔融键合,每个晶圆都有 CMP 滚降,然后基本上就是斜面。因此,如果你们将它们键合在一起,总会有一个区域没有完全填充。基本上有一个非常非常小的间隙,它会慢慢变为零。如果你现在开始研磨它,这个区域就会变得非常脆,因为修整基本上就像一把刀。因此,这种边缘控制以及如何管理它是目前的热门话题。”

其他人也同意这一观点。“根据不同的格式,应力可能导致两种主要的键合良率下降,”Bowers 说道。“在芯片到晶圆的键合中,芯片边缘的凸块非常容易受到应力的影响。如果设计人员无法改变应力分布,他们就必须改变设计规则,将 I/O 拉到芯片的中心。例如,在 HBM 的晶圆到晶圆键合中,晶圆外围的凸块最容易受到应力的影响。而且边缘的倒角很难控制,而且应力可能会加剧一些边缘损坏。

晶圆边缘修整是在晶圆对晶圆键合、体硅去除和 CMP 之前进行的。许多传统的 CMP 供应商都提供边缘修整工艺。

结论

晶圆边缘缺陷是制造过程中面临的一大挑战,目前正使用 CMP、干法或湿法蚀刻、边缘沉积和晶圆边缘修整来解决这一问题。尽管一些领先的设备制造商在生产中使用混合键合,但它仍然是一个相对不成熟且成本高昂的工艺。通过专门针对晶圆堆叠的工艺进行改进和优化,该行业的更多领域将能够使用这种技术。

Brewer Science 的 Smith 指出了一个潜在的改进。“对于混合键合,您需要减薄晶圆,然后将其释放。然后,您要将其键合到芯片或晶圆到晶圆。因此,您仍然需要减薄晶圆,首先将其解键合,然后需要清洁它。还有一些机制,您需要先将晶圆到晶圆键合,然后再减薄,但这还有待观察。我相信,最终我们将能够直接完成这些操作,从而省去一个工艺步骤,”他说。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。