进入高NA EUV光刻时代

在迎来高数值孔径极紫外光(high-NA EUV)微影时代之际,比利时微电子研究中心(imec)计算技术与系统/计算系统扩展高级副总裁Steven Scheer谈到了ASML-imec联合高NA EUV光刻实验室对半导体行业的意义。

他重点介绍了哪些应用将从过渡到高NA EUV 中受益,以及这种过渡将如何影响二氧化碳排放。展望未来,他解释了 imec 及其合作伙伴将如何进一步推动高 NA EUV 图案生态系统进入下一代。

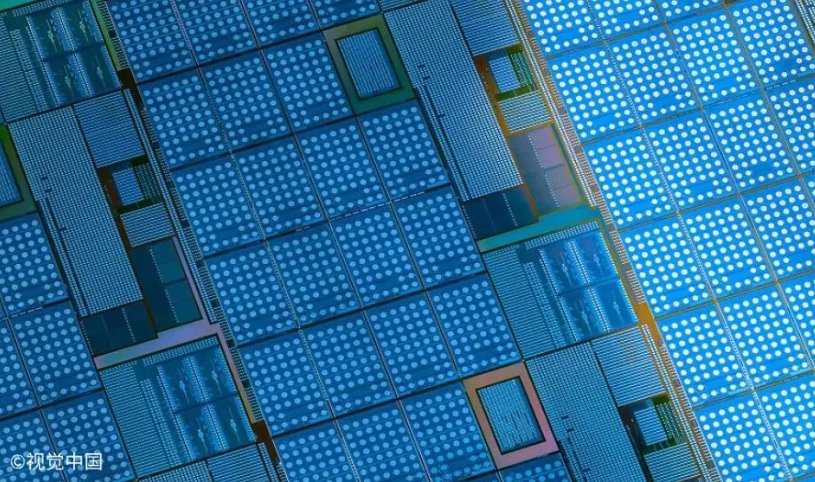

为大批量生产准备高 NA EUV

由ASML与imec联手在荷兰费尔德霍温建立的微影实验室正式启用,为推动High-NA EUV技术迈向量产立下了里程碑。存储和逻辑芯片的顶尖制造商现在可以使用首款0.55NA高数值孔径(high-NA)EUV曝光原型机TWINSCAN EXE:5000及周边基础设施,包含涂布及显影机、计量工具、晶圆及掩膜处理系统。在IDM及晶圆代工厂的晶圆厂房开始运作这些光刻机之前,imec与ASML将协助他们降低这项图形化技术的开发风险,并支援他们开发专有的High-NA EUV应用案例。

实验室未来也会开放给更广泛的供应商生态系统来使用。实验室的显影设施将能让他们在High-NA EUV专用材料与设备的工程设计领域成为先锋。实验室的第三类使用者则是imec及其先进图形化研究计划的几位伙伴,该计划推动图形化生态系统朝向High-NA EUV的下一代发展。

(SVP)Steven Scheer表示,费尔德霍温的High-NA EUV微影联合实验室的成立目标是加速High-NA EUV技术量产并提升其成本效益。ASML与蔡司(ZEISS)在短时间内已经成功开发high-NA EUV光刻机的专用解决方案,这些方案与光源、光学元件、镜头变形、拼接、缩短焦点深度(DOF)、边界放置误差及叠加精度有关。

同时,imec携手ASML及我们的广泛供应商网络密切合作,共同筹备0.55NA图形化生态系统如同imec在2024年国际光电工程学会(SPIE)先进微影成形技术会议(Advanced Lithography and Patterning Conference)所公布的消息。确保了用于第一代High-NA EUV的先进光刻胶、涂布底层材料、掩膜、量测技术、(变形)成像策略、光学邻近修正(OPC)与整合图形化及蚀刻技术都能如期供应。

这些筹备工作在近期促成了首批晶圆的曝光,10nm 和 16nm 宽的线/空间(即 20nm 和 32nm 间距)。现在原型光刻机和基础设施已经准备就绪,预计将在2025-2026 年投入大批量生产。

首例应用:14A逻辑芯片与D0a动态随机存取存储(DRAM)

Steven Scheer表示:“High NA EUV的首例应用会是14A(埃米)代逻辑芯片的量产,该技术节点将会以单次曝光完成24nm间距的金属导线/间隔(M0/M2层)图形化,甚至最终微缩到18nm间距。相较于现有的多重图形化0.33NA EUV制程,0.55NA单次曝光将能提高产率和缩短周期时间,甚至可能减少二氧化碳排放量。最终,这项技术会成为互补式场效电晶体(CFET)芯片的关键技术,为这种芯片的特殊复杂结构生产图形。”

存储的芯片制造则会随后导入这项技术,用来生产动态随机存取存储(DRAM)的最关键元件结构。High-NA EUV技术估计将能通过单次曝光来生产电荷储存节点连接垫(storage node landing pad)与位元线周边的图形。2D动态随机存取存储(DRAM)的D0a技术代会是第一个应用契机,所需的中心间距为28nm。

迈向下一代High-NA EUV

Steven Scheer指出,尽管先进半导体生态系统的目标是在短期内把High-NA EUV技术引进量产,但是imec及其伙伴看得更为长远,旨在实现下一代高 NA EUV。为了这些研发活动,由imec与ASML合建的High-NA EUV微影实验室将作为imec设施的虚拟延伸。虽然曝光会在荷兰费尔德霍温进行,但是前处理与后处理的部分工作仍将在imec的12寸晶圆无尘室进行。

首先,我们会密切监测High-NA EUV微影设备(cluster)原型机的性能,束型机即相连的光刻机与显影机。为此,imec目前持续在制备专用的晶圆堆叠,基线制程也正在转移到High-NA EUV束型原型机上。我们的团队将会评估束型机的最高解析度(最终目标是实现导线/间隔的金属间距为18nm、接触孔洞间距为28nm)、稳定性(例如经过曝光后的关键尺寸稳定度与结构缺陷密度)以及有效焦点深度(DOF)。因为这种机台的数值孔径更高,其焦点深度(DOF)预计会比0.33NA EUV设备还要小两到三倍,这也是0.55NA EUV设备所用的光阻薄膜更薄的原因之一。

此外,我们也携手计量领域的伙伴,在联合实验室开发并安装了专用检测工具,以监测和改善图案结构的缺陷率。一直以来,电子束检测都被选为研究超小型接触孔洞表面缺陷的主要工具。我们希望能实现业界的远大目标:每测量一百万个接触孔时,把每个接触孔的缺陷数量控制在只有一个。在金属导线/间隔方面,光学检测工具则与电子束整合,以侦测和分类缺陷,并引导实现每立方公分只有不到一个缺陷的目标。

最后,逻辑与DRAM应用案例也正在酝酿。更大的工艺模块将接受图像分辨率和缺陷率方面的检查,例如使用检测工具和电气测试的组合。

扩展0.33NA EUV业务。促使高低数值孔径双获益

Steven Scheer表示,在我们的无尘室,最新一代的0.33NA EUV光刻机仍是用来协助优化新代High-NA EUV图形化生态系统的辅助工具组。另外,并非所有的芯片功能都需要High-NA EUV技术。试想元件中间与全域的芯片内连导线,因此,我们也持续改良0.33NA EUV生态系统。除此之外,0.33NA与0.55NA曝光技术还有一些常见的挑战,像是对改良版光刻胶的需求。

“0.33NA 扩展活动”的重点领域之一是高 NA EUV 的场拼接。场拼接的必要性源于引入变形镜头(即在 x 和 y 方向上具有不同缩小倍率的镜头)与不变的掩模空白尺寸(仅允许晶圆上的半场尺寸)相结合。在 2024 年 SPIE 高级光刻 + 图案会议上,imec 分享了其在实现分辨率场拼接方面的最新见解,这减少了为应对场尺寸减小而进行设计更改的需要 。这项工作是在 imec 洁净室的 NXE:3400C 扫描仪上进行的,与 ASML 和我们的掩模合作伙伴合作。

另一个关键议题是光刻胶和涂布底层显影。imec携手光刻胶供应商,目前正在筛选替代的光阻材料,并根据表面缺陷、粗糙度与阻剂减量来衡量这些材料的表现。化学放大光刻胶 (CAR)已一直主导着光学光刻领域,未来也会持续在选定的应用案例占有优势。

然而,High-NA EUV可能会颠覆金属氧化物阻剂(MOR)的发展,这种光刻胶在高解析度导线/间隔与小型六方柱结构的方面一直展现良好的微影性能。为了解这些金属氧化物阻剂如何与极紫外光线发生作用而进行基础调查将能让我们克服现存的挑战,例如这些光刻胶的性能稳定度。我们也会研究与这些光刻胶匹配的涂布底层,以提升其附着力。此外,选配涂布底层和光阻材料的组合还能有机会进一步减少曝光刻胶,进而降低(High-NA)EUV的曝光成本。

我们专注于定向自组装 (DSA),它使用嵌段共聚物 (BCP) 的微分离来定义图案。业界对将 DSA 与 EUV 结合使用很感兴趣,因为它能够降低粗糙度、修复缺陷并降低 EUV 剂量。我们的目标是进一步降低 DSA 图案内的缺陷率。从长远来看,我们将把 DSA开发扩展到高 NA EUV。为了与高 NA EUV 相关,我们必须将 DSA 图案缩小到 24nm 间距以下。由于目前使用的 PS- b -PMMA 型嵌段共聚物无法实现这一点,因此我们已与 DSA 材料供应商一起开始研究所谓的高 χ BCP。

Hyper-NA EUV:光刻技术的明日之星?

虽然现在把超高数值孔径紫外光(Hyper-NA EUV)称作明日之星,着实言之过早,但是imec与ASML已经开始进行相关的可行性研究。Hyper-NA的数值孔径可以高达0.75-0.85,可能成为 0.55NA EUV 的继任者,使业界能够打印间距远低于 20nm 的线条/空间,从而避免重新依赖高 NA EUV 多重图案化。

这项技术能否成为现实,将取决于行业需求,以及克服技术障碍的能力。举例来说,imec正在通过模拟来研究运用Hyper-NA EUV进行成像的可行性。问题之一是景深的进一步减小,景深的减小与 NA 的平方成反比。目前可用的总景深对行业来说是否仍然可行,我们该如何处理这些受限的景深资源?但最终,与前几代光学光刻技术一样,决策也将取决于成本可以降低的程度。关键在于找到经济上的最佳平衡点——引入新技术的成本和收益开始超过“旧”技术带来的日益增加的挑战的时间点。

减少二氧化碳当量足迹

Steven Scheer表示,我们运用了自家的虚拟晶圆厂模型imec.netzero来量化从low-NA多重图形化转移到High-NA EUV单次曝光的环境影响。二氧化碳排放的一个主要来源是微影时的电力消耗。我们的模型显示,在单次曝光时,0.55NA光刻机EXE:5200所消耗的电力多过0.33NA光刻机NXE:380,这是在假设极紫外光源和晶圆产量相同的情况下。这主要是因为晶圆平台及掩膜平台的速度必须加快,才能在High NA EUV的曝光长度更短的情况下维持产量。曝光之所以受限是源于更高数值孔径所用的变形镜片。

尽管高数值孔径光刻机的功耗更高,但我们的模型显示,把一次low-NA EUV双微影蚀刻(LELE)制程模组改为High-NA EUV单次曝光能降低30%二氧化碳总排放量。简化制程的影响胜过加速制程平台相关的功耗增加。通过最大程度提高光刻机的产量就能控制功耗,产量即机台每小时产出的晶圆数量(wph)。减少光刻胶量并管理晶粒大小/掩膜布局都是维持最大产量的关键,因为这两者影响着High-NA EUV光刻机完成晶圆曝光所需的时间。

除了光刻之外,蚀刻工艺也是直接二氧化碳排放的重要来源。大多数干蚀刻工艺都依赖于氟化合物,而氟化合物的全球变暖潜能值比二氧化碳高得多。我们开发工艺和设计方向以减少这些氟化合物的排放。

除了排放之外,还有其他值得关注的领域,例如材料稀缺和 PFAS 等有毒物质的使用。PFAS是半导体制造多个方面的内在推动因素,包括CAR和冲洗材料。高 NA EUV 可能标志着不含 PFAS 的 MOR 的引入。我们最近展示了在薄 MOR 光刻胶中图案化小线条/空间的良好性能,以及使用带有二元明场掩模的 MOR 光刻胶图案化接触孔的良好性能。但 CAR 仍将是图案化不太重要的芯片特征的主力。我们与供应商社区一起,发起了新的研究计划,探索不含 PFAS 或限量 PFAS 的替代品,并对其性能进行基准测试。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。