Chiplet标准走向3D

目前,管理小芯片技术的标准已经历了第二次迭代。

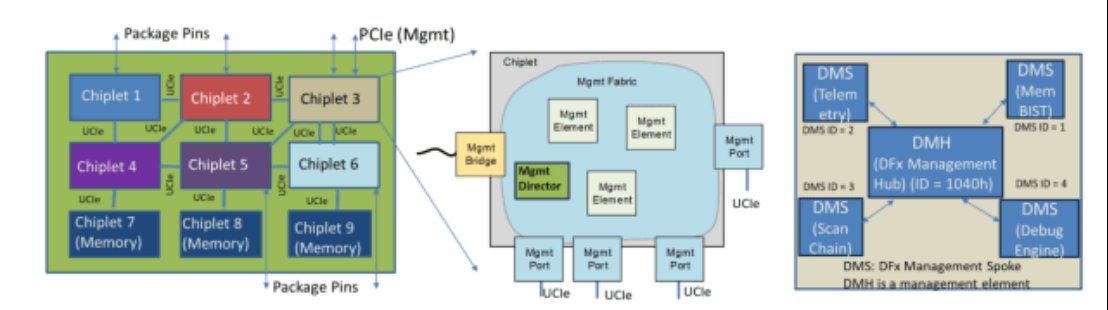

通用芯片互连快速 (UCIe) 联盟成立于 2022 年 3 月,最近发布了 2.0 规范,其中的更新解决了跨多个芯片的 SiP 生命周期的可测试性、可管理性和调试 (DFx) 设计挑战。更新的一个关键特性是支持 3D 封装,使芯片能够大幅提高带宽密度和功率效率。

联盟主席 Debendra Das Sharma 表示,UCIe 2.0 规范完全向后兼容,同时引入了可选的可管理性功能和支持与供应商无关的芯片互操作性的 UCIe DFx 架构 (UDA)。

该联盟已将规范制定工作分散到多个工作组,这些工作组侧重于不同的方面,包括电气、协议、外形尺寸和合规性、可管理性和安全性以及系统和软件。Das Sharma 表示,最近成立的汽车工作组反映了该行业对开始收集需求的兴趣。

他将UCIe 1.0 描述为平面互连,因为它支持 2D 和 2.5D,这意味着芯片并排排列。新规范通过解决必要的连接问题,支持芯片垂直堆叠 3D。

Das Sharma 表示,UCIe 2.0 中的其他重要更新与可管理性有关,包括调试和测试,既包括基于芯片的调试和测试,也包括芯片封装后的调试和测试。2.0 中的另一个新功能是针对互操作性和合规性测试优化的封装设计。

UCIe 2.0 支持的管理机制包括发现芯片及其配置、电源和热管理、错误报告以及芯片安全的各个方面。Das Sharma 表示,这些机制利用现有的适用行业标准,并且与芯片上的底层协议无关。这些机制还旨在跨不同供应商的芯片工作,并支持特定于供应商的扩展。

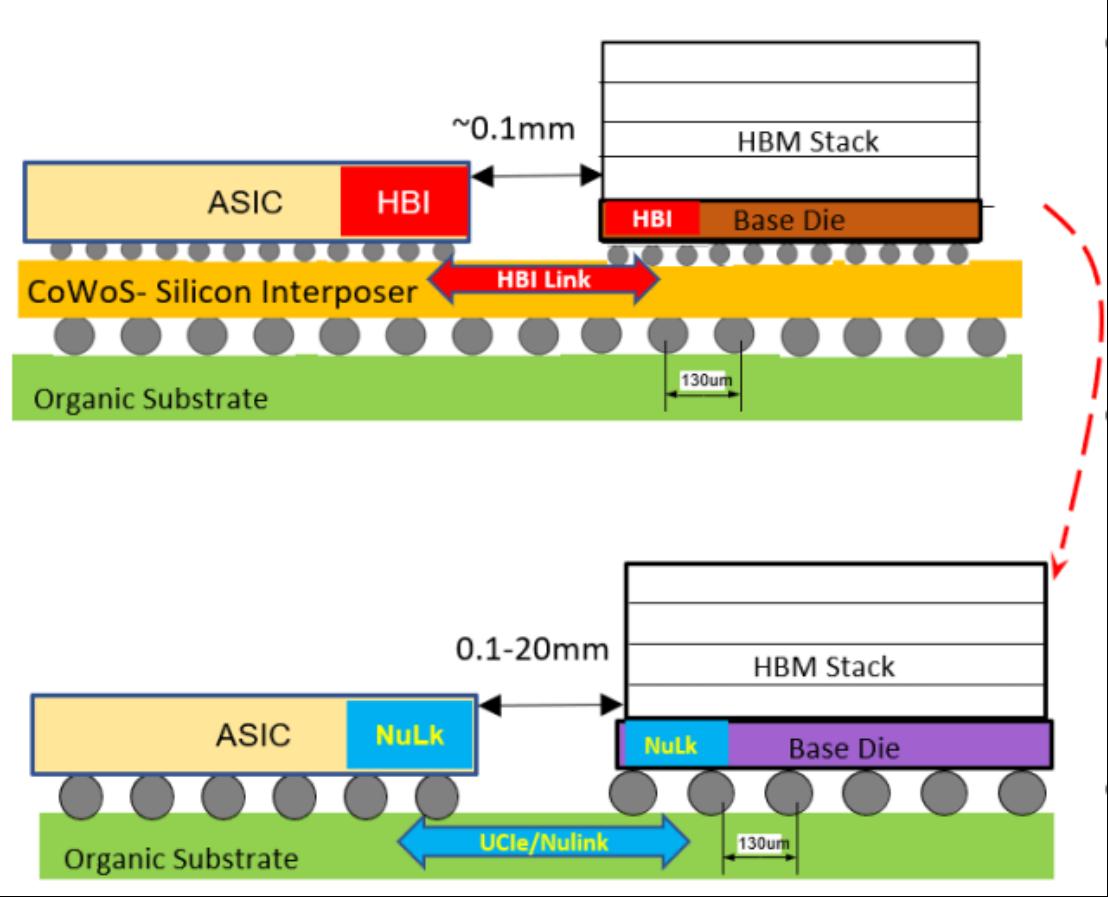

他补充说,芯片的 3D 趋势之一是转向混合键合,这正变得越来越主流,并允许大幅缩小芯片之间的凸块间距。3D 互连几乎完全消除了芯片之间的距离,这意味着互操作性必须限制在相同的凸块间距内。

UCIe-3D 针对混合键合进行了优化,凸点间距从大到 10-25 微米到小到 1 微米或更小,以提供灵活性和可扩展性。

Das Sharma 表示,较短的互连距离会影响电源效率。“由于没有任何寄生效应,即使在芯片内部,功耗也会显著降低,”他说。“这是一个非常简单的电路。”

Das Sharma 表示,UCIe 正在追随 PCI Express 和以太网等更成熟的互连技术的脚步,希望通过实现两位数的改进来提高带宽密度,同时优化电源效率。

小芯片技术并非新鲜事物,但直到最近几年,它的普及才推动了对最佳实践、标准和工具的需求。2022 年底,硅谷初创公司 Eliyan Corporation提供了一种更高效的封装方法。其“线束”(BoW) 小芯片系统旨在通过使用标准封装实现与使用先进封装技术的芯片到芯片实现类似的带宽、功率效率和延迟。

硅谷初创公司 Eliyan 的 BoW 芯片系统旨在实现与 die-to-die 实现类似的带宽、功率效率和延迟。(来源:Eliyan)

硅谷初创公司 Eliyan 的 BoW 芯片系统旨在实现与 die-to-die 实现类似的带宽、功率效率和延迟。(来源:Eliyan)

最近,在 2024 年 6 月,另一家 Chiplet 初创公司帮助消除 Chiplet 系统设计的复杂性。Baya Systems 的算法驱动系统架构平台WeaverPro 与其可扩展 IP 和缓存结构 Weave IP 相结合,通过数据驱动的设计和优化将构建 Chiplet 架构的所有步骤整合在一起,以加速 Chiplet 的分析、设计和部署。

Das Sharma 表示,UCIe 2.0 将致力于向后兼容 1.0 规范版本,并与 PCIe 和 NVMe 等更成熟的互连协议保持一致。

不过,虽然这些成熟的互连协议已经确定了每三年更新一次的节奏,甚至 CXL在短时间内迅速出现三次迭代后也可能遵循相同的模式,但 Das Sharma 表示,目前尚不清楚 UCIe 将如何稳定下来。

他说,新版本的许多工作组都有很多事情要做。“目前,我们并不缺乏真正令人兴奋的使用模型和需要解决的问题。”

随着数据中心和云计算业务的快速增长,对芯片的性能、功耗和成本提出了更高的要求。3D Chiplet 技术可以为数据中心提供更高性能、更低功耗的服务器芯片,满足数据处理和存储的需求。例如,英特尔、AMD 等公司已经在数据中心芯片中采用了 Chiplet 技术,并不断探索向 3D 方向发展。另外,人工智能和机器学习算法需要大量的计算资源,对芯片的算力和带宽要求极高。3D Chiplet 技术可以将多个高性能的计算芯片和存储芯片集成在一起,为人工智能和机器学习提供强大的计算能力。例如,英伟达的 GPU 芯片在采用 Chiplet 技术后,性能得到了显著提升。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。