复旦大学实现0.64nm等效电容厚度栅介质集成

在晶体管的微缩技术路线中维持栅极对沟道的有效调控是根本性需求。因此,导电层厚度必须随长度同步减薄。然而当传统材料在厚度减薄至5 nm尺度以下时,会遭遇严重的表面散射与迁移率骤降,这种微缩瓶颈是晶体管无法延续摩尔定律的主要原因。

凭借原子级厚度(< 1 nm)与高迁移率优势,原子层半导体被国际器件与系统路线图(IRDS)预测为到2029年仍能延续摩尔定律的关键材料。然而,将其整合进现有的CMOS工艺面临严峻阻碍:惰性范德华表面因缺乏活性位点,导致传统介质沉积工艺难以生长高质量、连续的超薄高介电常数的介质。这一界面集成难题成为了制约二维电子器件走向工程化应用的核心壁垒。

针对这一重大关键技术问题,复旦大学集成电路与微纳电子创新学院周鹏-刘春森团队通过原位诱导单层半导体均匀氧化,与本征氧化的Si/SiO(2)类似,将惰性的单原子层材料构筑为晶圆级超薄介质,实现了半导体与高介电常数栅介质的高良率集成,并成功将电容等效厚度(CET)降至0.64 nm,显著低于国际器件与系统路线图2 nm节点对栅介质CET的要求(< 1 nm),为未来先进制程下的器件微缩预留了充足的性能空间。相关成果以《晶圆级单层介质与原子级厚度半导体的集成》(“Wafer-scale monolayer dielectric integration on atomically thin semiconductors”)为题发表于国际顶尖期刊《自然-材料学》(Nature Materials)。

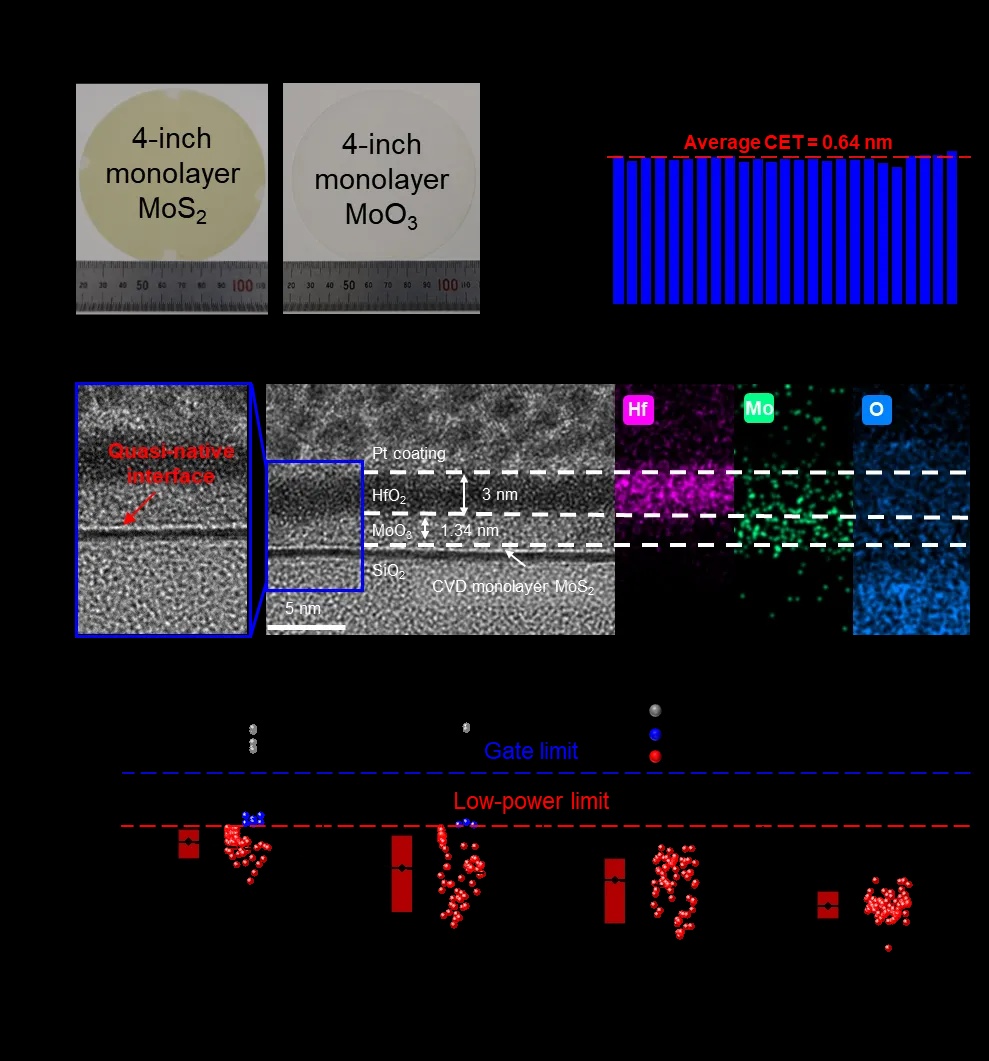

图1(a)晶圆级单层MoS(2)向MoO(3)转化的光学图片;(b)单层MoO(3)的CET统计数据;(c)单层MoO(3)与超薄HfO(2)集成的TEM图;(d)不同CET下MoO(3)/HfO(2)叠层的漏电流密度统计。

研究团队提出了一种面向CMOS兼容的单原子层半导体与超薄介质集成策略:通过对具有惰性表面的单层MoS(2)实施均匀氧化,在晶圆尺度上实现了原子级平整的超薄MoO(3)介质层,解决了高介电常数介质沉积时前驱体无法在其表面均匀成核的问题。 此外,研究人员进一步展示了该原位氧化介质在实际器件中的集成潜力。单层MoO(3)可通过CMOS兼容工艺与经典材料(如HfO(2))构建介质叠层,并在满足IRDS 2 nm节点对介质CET的要求下,实现了92.2%的超高良率。采用该栅叠层的顶栅晶体管表现出优异的电学调控能力:CET为0.96 nm,工作电压范围内栅极漏电流低于1 pA,开关比超过10(8)。

更进一步,研究团队还验证了单独使用单层MoO(3)作为顶栅介质的极限性能。当MoO(3)作为唯一栅介质时,其晶体管的CET可低至0.64 nm,远低于IRDS 2 nm节点对介质的要求。实验结果表明,器件在整个工作区间内,栅极漏电流密度满足低功耗要求(1.5×10(2) A/cm(2))。 与此同时,晶体管展现出足以适配逻辑电路应用的开关比,关态电流(I(off))低于IRDS高密度与高性能应用的限值。该成果为在原子层半导体上原位集成超低CET介质提供了一种极具潜力的技术路径。

复旦大学集成芯片与系统全国重点实验室、芯片与系统前沿技术研究院刘春森研究员和集成电路与微纳电子创新学院周鹏教授为论文通讯作者,博士生沈桢贞、吴昊奇和刘春森研究员为论文第一作者。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。