高密度三维动态随机存储器,取得重要进展

在半导体存储技术领域,DRAM作为计算系统的关键组成部分,一直面临着提升密度与降低功耗的双重挑战。随着人工智能与大数据的快速发展,传统存储架构已难以满足日益增长的数据处理需求。在主流1T1C架构中,制程微缩导致存储电容难以进一步缩小,电容器漏电与干扰问题日益凸显。2T0C架构虽被视为潜在解决方案,但传统集成方法因采用分步堆叠工艺,面临着横向对准偏差与热循环效应带来的严苛挑战。

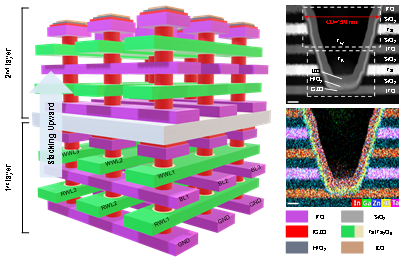

针对上述挑战,微电子所集成电路制造技术全国重点实验室研究团队联合北京超弦存储器研究院、山东大学提出一种新型双栅4F² 2T0C存储单元。该技术通过原位金属自氧化工艺,实现4F²存储单元中读取晶体管和写入晶体管的自对准集成,并可通过多值存储技术进一步提升存储密度。

本研究以“High-density three-dimensional integration of dynamic random-access memory using vertical dual-gate IGZO TFTs”为题发表在Nature Communications期刊上,微电子所博士后廖福锡、北京超弦存储器研究院朱正勇研究员、微电子所博士生李子涵为共同第一作者,微电子所李泠研究员、杨冠华副研究员、北京超弦存储器研究院赵超研究员、山东大学Arokia Nathan教授为共同通讯作者。

动态随机存取存储器的三维集成面临着严峻挑战,这些挑战与横向错位以及因单独堆叠工艺导致的热循环有关。为解决单元错位和热循环问题,研究团队采用了单步工艺同时堆叠双栅极铟镓锌氧化物晶体管。通过原位臭氧氧化方法优化接触金属化及其界面,垂直双栅极晶体管展现出高导通电流、小亚阈值斜率以及高热稳定性和器件均一性。

新型双栅4F² 2T0C存储单元具有以下优势,一是通过自对准单步(SASS)工艺实现4F²的位单元面积,二是双栅结构消除了典型的不可靠读取问题和IR压降问题。

4F²双栅2T0C存储阵列示意图和电镜表征

测试结果表明,该垂直双栅晶体管实现了优异的开态电流与亚阈值摆幅,并在85℃热稳定性测试中取得-22.6 mV(NBTS)与87.7 mV(PBTS)的可靠表现,兼具高性能与高稳定性。基于该晶体管的4F² 2T0C单元支持4比特多值存储,实现了50纳秒的写入时间,数据保持时间超过300秒,展现出良好的技术潜力。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。