印度研发出用于神经形态计算的分子忆阻器

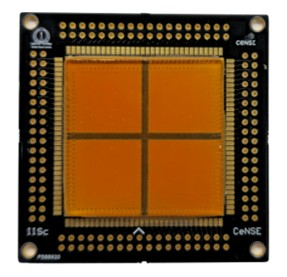

印度班加罗尔科学学院(IISc)纳米科学与工程中心(CeNSE)在 Navakanta Bhat 教授与 Sreetosh Goswami 副教授的带领下,研制出一款基于钌化合物的分子忆阻器。该器件据称可实现14位模拟精度,能效达4.1 TOPS/W,能够实现线性权重更新,提升信号处理场景下神经形态计算的能效。

研究人员通俗解释称,他们构建了一种可模拟微型、低功耗神经元突触的分子,并将数百万个此类分子排布成阵列,以类似人脑的方式执行AI计算,而能耗仅为传统方案的零头。该钌配合物采用偶氮芳香配体(经过精细设计的有机环),呈现零级动力学特性,意味着开关过程以恒定、可预测的速率发生,不受外界条件影响。这使其实现了14位精度,并能在四个数量级范围内实现线性、对称的电导更新。

研究人员表示,该技术可支撑边缘AI应用中的神经形态计算,这类场景受功耗与延迟限制,难以使用传统基于 GPU 的系统。IISc 班加罗尔分校的 Bhat 与 Goswami 表示,他们正通过CeNSE孵化的一家初创公司开发原型芯片。该芯片预计一年内推出,采用22纳米工艺与交叉阵列架构,实现存内计算。

研发背景

现有AI系统受能耗问题制约,卷积神经网络(CNN)约 94% 的能耗被用于动态随机存取存储器(DRAM)访问,而非计算本身。传统芯片需分步执行AI运算,随着模型规模扩大,运算步骤也随之增加。

半导体行业专家、前 MIPS 首席运营官 Ashok Balivada表示:“边缘AI既需要高性能,又必须控制功耗。现有方案大多只是渐进式改进。数字技术需要精细设计才能管控功耗,虽然已有存内计算与近存计算方案,但仍属于逐步演进。”

英特尔 Loihi 是面向脉冲神经网络的实验性神经形态计算芯片。Groq 的 LPU、IBM NorthPole 等数字AI加速器均采用大型片上数字设计实现快速、高能效推理,其中 NorthPole 部分借鉴了人脑架构。印度理工学院孟买分校(IIT Bombay)致力于忆阻器的大规模可靠集成与布线,而 IISc 班加罗尔分校则从底层研发性能更优的忆阻器材料。

Balivada表示,IISc 班加罗尔分校的这项研究融合了三大方向:新材料、模拟计算与类脑架构。“其核心是高效执行矩阵乘法及相关运算,功耗优势来自模拟技术。” 他补充道,该设计仍需融入标准 CMOS 流程,基础系统保持数字架构。

Goswami称,这项研究源于现有计算模型的局限,从材料到架构多个层面重新审视传统设计思路,同时保持与硅基制造工艺兼容。Bhat补充说,团队正在 CeNSE 孵化初创公司并组建团队,推动技术商业化。“我们相信一年内将推出最小可行产品。” 他表示,芯片计划采用台积电22纳米工艺流片。

神经形态芯片工作原理

这款在研芯片定位为AI推理加速器。Balivada表示,项目主要有两大目标:将分子忆阻器实现单片集成,并整合至数模混合片上系统(SoC)。“未来产品必须采用单片方案,分立实现难以满足成本等要求。”芯片包含模拟前端设计、数字数据通路与片上静态随机存取存储器(SRAM),系统设计用于运行图像分类、目标检测、语音交互等任务。“该器件将作为AI加速器,连接笔记本电脑、台式机等主机设备。”

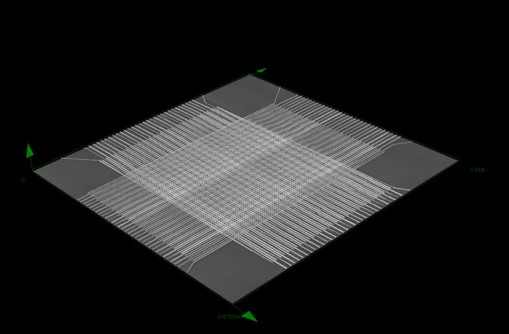

神经形态芯片采用交叉阵列架构,电压与电流可物理并行完成矩阵运算,将原本呈二次方增长的运算量压缩为单次并行操作。Bhat 解释称,系统利用基础电学原理实现乘累加(MAC)运算。“矩阵以电导形式存储,输入以电压形式施加,电压与电导的乘积产生电流,即完成乘法运算。” 多个单元的电流依据基尔霍夫电流定律沿导线汇总,完成累加步骤。“原本需要数千次数字 MAC 运算的操作,可瞬间完成。”

Goswami 补充说,系统设计需要平衡模拟与数字运算。“即便占AI计算主体的向量矩阵乘法 99% 都被加速,剩余 1% 仍可能消耗大量功耗。”IISc 团队正致力于模拟计算与数字控制的接口、更高程度的片上存储集成,以及算法与硬件协同设计,以应对模拟噪声与精度降低问题。

芯片物理架构

与多数现有存储技术不同,该材料不依赖缺陷工作。Goswami表示,“如果系统基于缺陷,过程就会具有随机性,而模拟电路不希望出现随机特性。我们的材料具有确定性,可精准编程至目标状态。”

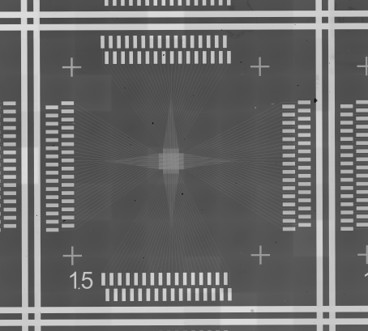

分子薄膜厚度约 60 纳米,大约是人类头发丝直径的千分之一。Goswami 表示,在原子层面,系统依靠离子在分子位点间移动工作。“每种构型对应不同的电子传输水平,形成稳定的存储状态。”该器件面积可从 1 微米缩至数十纳米。Bhat 称,这种缩放可提升密度,而厚度保持在 70 纳米左右不变。Goswami 补充道,即便尺寸缩小,器件仍能保持可用精度。“14 位精度的器件在 50 纳米尺寸下仍可实现约 11 位精度,对 8 位推理而言完全够用。”

研究团队表示,钌元素供应充足,不存在供应链约束,同时也在探索铁、钴基替代材料。“这类材料已有相关研究储备。”Goswami 说。

在忆阻器存储状态可靠性方面,团队实现了数月稳定运行。“我们对编程后的状态进行了七八个月的测试,性能未出现变化。”Goswami 表示,器件 endurance 测试已达 10⁹次循环,而闪存约为 10⁶次。Bhat称,采用 CMOS 制造中的标准钝化工艺后,电导可保持稳定。“电导一旦设定,可长期保持不变。”

该芯片设计目前瞄准 8 位精度,也支持 4 位运算以降低功耗。数据转换器速度约为 100 兆样本 / 秒,吞吐量可通过并行化扩展。

未来规划

Balivada表示,芯片目前处于 RTL 设计阶段,团队使用新思科技、楷登科技、西门子的 EDA 工具,部分组件复用现有设计,数据转换器等模块正在开发中,同时借助 PyTorch、TensorFlow 等框架开展 workload 验证。该技术已申请多项专利保护。“核心是材料专利,同时在架构与系统层面也拥有专利。”Bhat 说,初创公司将从 IISc 获得专利授权。

在产业合作方面,Balivada称团队计划在芯片就绪后提供测试样片,预计与系统开发商、客户及高校展开合作,同时正与印度国防研究与发展组织(DRDO)合作开发特定应用。尽管在集成与设计知识产权获取方面仍存挑战,但团队表示不存在根本性技术障碍。“我们拥有清晰的技术路径,关键在于落地执行。”Bhat 说。Balivada补充道,将技术融入商业制造流程具备可行性,“该工艺位于后段制程,不会干扰前段晶体管工艺。”

目前神经形态计算仍是小众市场,2025 年规模约2.13亿美元,但随着类脑AI架构需求增长,预计到 2034 年将增长七倍以上,达到约16亿美元。IISc 班加罗尔分校团队聚焦边缘AI推理的 SoC 集成,包括交叉阵列扩容与器件尺寸微缩。中期目标是提升模拟运算比例与高密度片上非易失性存储,长期目标则是实现基于反向传播的片上训练。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。