下一代AI SoC,关键在NoC

面向人工智能负载的现代SoC设计,已从根本上改变了NoC的定位,它不再只是简单的互联结构,而是决定系统性能、功耗与可扩展性的核心架构要素。随着计算密度提升、异构加速器大量普及,数据传输愈发成为支配系统整体表现的关键因素。因此,NoC架构必须被视为首要设计决策,而非后期集成环节。现代AI SoC的瓶颈并非计算本身,而是仲裁、内存访问与互联带宽,这使得NoC拓扑、缓存机制与服务质量(QoS)策略成为达成目标性能指标的关键。

以人工智能为核心的SoC,在流量特征与集成复杂度上均与传统设计存在差异。当前系统集成了中央处理器(CPU)、图形处理器(GPU)、神经网络处理器(NPU)、数字信号处理器(DSP)及各类领域专用加速器,会产生突发性强、并发度高的流量模式,且对资源竞争与尾部延迟极为敏感。这些特征对传统总线架构构成挑战,亟需具备可扩展性的NoC拓扑,在吞吐量与延迟之间实现平衡。此外,先进工艺节点会加剧连线延迟与布线拥塞,使得物理实现约束与架构决策紧密绑定。因此,拓扑选择必须同时兼顾逻辑跳数与布局可行性,过长的物理互联可能会抵消理论上的性能优势。

AI SoC中最重要的架构决策之一,是一致性模型。硬件缓存一致性可简化编程,但会带来一致性流量与可扩展性难题,尤其在侦听机制与目录机制下更为突出。与之相对,软件管理的一致性能降低硬件复杂度,让加速器行为更具确定性,但会增加编译器与运行时开销。专用人工智能加速器通常倾向于采用软件管理内存,以最大限度减少不可预测的延迟;而异构SoC则普遍采用混合方案,以保持与传统 CPU 集群的兼容性。一致性方案的选择直接影响NoC流量特征、仲裁逻辑与内存层级结构,这也表明互联架构无法与系统级内存决策割裂开来。

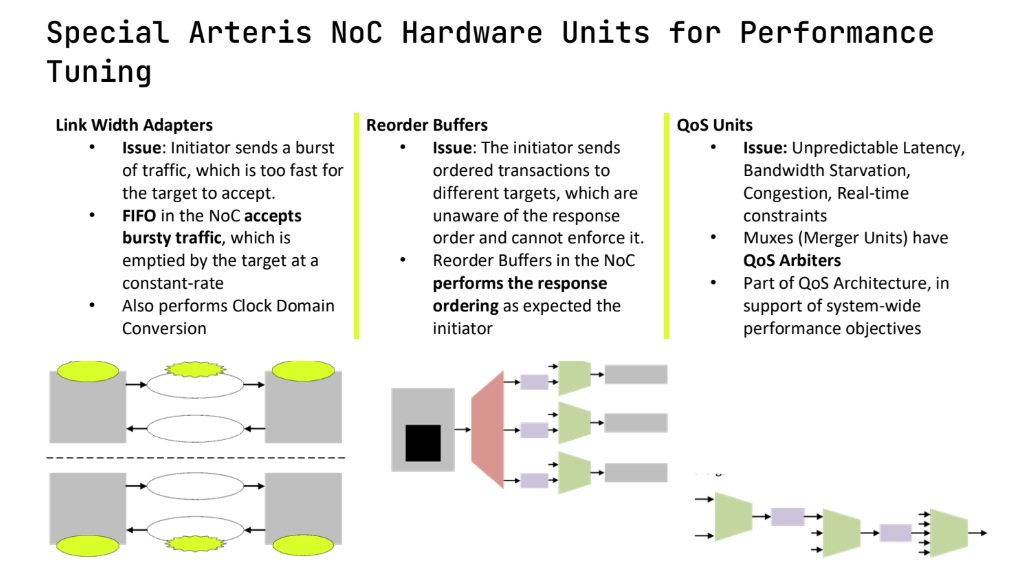

除拓扑与一致性外,专用NoC硬件单元对处理混合负载至关重要。链路宽度适配器可实现突发吸收与时钟域跨接,重排序缓存保障多目标事务的执行顺序,服务质量仲裁逻辑则确保对延迟敏感的流量优先于批量传输。这些特性有助于在高负载下维持可预测的延迟,对同时承载控制流量与大规模张量数据传输的人工智能系统尤为关键。若服务质量策略设计不当,关键实时事务可能出现资源饥饿,导致性能波动、系统效率下降。

物理布局规划同样在NoC设计中占据重要地位。集中式互联虽能简化逻辑复杂度,却易引发布线拥塞与时序收敛风险;而分布式NoC方案更适配分区布局,可缩短长线长度。因此,早期架构建模需纳入符合实际物理条件的假设,包括时钟域、电源分区与IP布局。忽视这些因素往往会导致后期重新设计,增加项目进度风险与工程成本。

规范化的NoC开发流程可进一步降低实现风险。高效设计流程始于流量建模与高层性能分析,继而开展拓扑探索、布局适配、时序收敛所需的流水线插入,并通过物理综合约束完成验证。架构建模与物理实现之间的迭代反馈,能让设计人员在交付寄存器传输级(RTL)代码前确定可行方案。拓扑生成工具等自动化框架可将布局感知能力融入探索过程,进一步提升设计效率、缩短连线长度并优化延迟。

随着SoC规模扩展,受电源域、时钟孤岛与组织边界限制,物理分区已不可避免。分区式NoC需在保障互联的同时,支持电源切换过程中的隔离、保持与复位序列。跨域协调这些行为复杂度极高,必须在早期规划中解决,以避免功能与验证问题。合理规划可确保NoC在低功耗状态与唤醒流程中正常运行,不出现死锁或数据损坏。

为现代AI SoC设计NoC,需要综合考量流量特征、一致性模型、拓扑结构、服务质量机制、物理布局与电源管理。将NoC视作系统级设计问题,而非事后补充的互联方案,才能在日益复杂的异构芯片平台中,实现可扩展的性能、高效的功耗控制与可预期的项目实施周期。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。