3D IC设计的多物理场挑战与破局路径

对于采用 3D IC 架构的设计团队而言,在持续追求性能与可靠性的过程中,会遇到一系列熟悉却愈发复杂的挑战:如何在这类堆叠架构中管理功耗、散出热量,并应对各类物理效应之间的复杂相互作用?3D IC 虽在尺寸、性能、功耗效率与成本上具备显著优势,但也带来了更高层级的设计复杂度。想要妥善应对这些挑战,尤其是在功耗管理、热耗散以及各类物理现象复杂耦合方面,需要采用更精密的设计方法。

3D IC 带来的挑战日益严峻

从传统 2D SoC架构转向异构集成与完整 3D 堆叠,从根本上改变了设计格局。2D 设计主要依靠成熟的工艺设计套件(PDK)即可获得可预测的结果,而 3D IC 则引入了新型材料、海量数据以及复杂的交互效应。设计人员再也无法将机械、热学与功耗等物理效应抽象忽略,这些因素已成为实现高可靠性设计的核心。

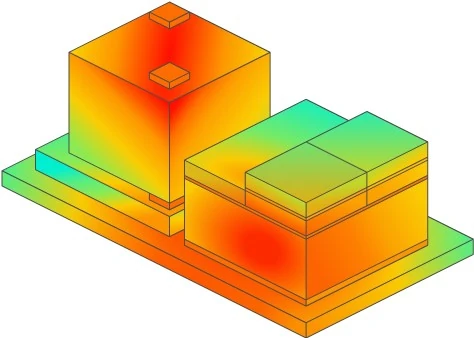

以功耗与热量的基本关系为例:功耗会直接产生热量,而热量又会导致金属线形变、改变晶体管特性。这些变化会在设计中连锁传导,迫使设计人员重新估算功耗、再次进行时序分析。将多个裸片、小芯片与元器件堆叠在紧凑封装内,会进一步加剧这种复杂度。图 1 展示了 3D 堆叠结构中的热热点分布。

图 1:3D 堆叠中的应力热点涉及热、电与机械多重效应。

以往熟知的 “Known Good Die” 概念,现已升级为 “ Known Good Stack”,一处失效就可能危及整个系统的可靠性。这种 “多物理场耦合” 意味着各类物理现象会同时影响设计的物理结构与电气性能。若未审慎考量这些效应,可能引发严重的良率问题,甚至导致产品在实际应用中出现可靠性故障。这类问题既包括电迁移(EM)、寄生参数提取(PEX)、电压降(IR)、静电放电(ESD)等传统问题,还叠加了新型热学与机械交互带来的新风险。

尽管这些单一问题大多已被业界熟知,但传统 SoC 设计与验证方法在 3D IC 层面往往不再适用。原因在于 3D IC 引入了与 2D IC 中传统硅、玻璃、铜组合特性截然不同的新材料。更复杂的是,这些效应无法孤立分析,一个参数的变化会牵动其他参数,形成高度关联的复杂体系。

协作与统一语言:可靠集成的基础

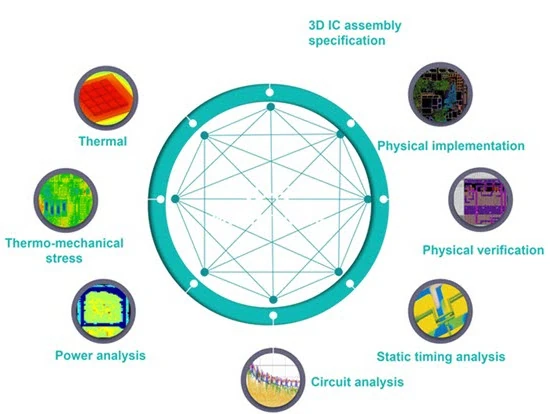

除技术复杂度外,成功的 3D IC 项目还依赖芯片设计人员、封装工程师、代工厂合作伙伴以及半导体外包封装测试(OSAT)厂商等多团队的紧密协作。在严格保护核心知识产权与工艺数据的前提下,建立统一的设计语言与可互通的设计流程同样至关重要。更紧密的集成能让跨职能团队在设计周期早期识别并解决风险,避免在设计签核阶段付出高昂的整改成本。图 2 展示了 3D IC 设计与验证流程中的各类关联分析环节。

图 2:成功实现 3D IC 设计所需的各类分析相互关联。

以往的多物理场分析常采用简化的封装级模型,多将裸片视作均质单元或 “实体块”。但近年研究表明,功耗、热与机械应力会显著偏离裸片级的预期表现。这凸显出在设计初期就让裸片设计人员参与多物理场指标讨论的必要性。在设计周期早期,布局与材料选择的灵活度最高,这也印证了左移设计思路的重要性。

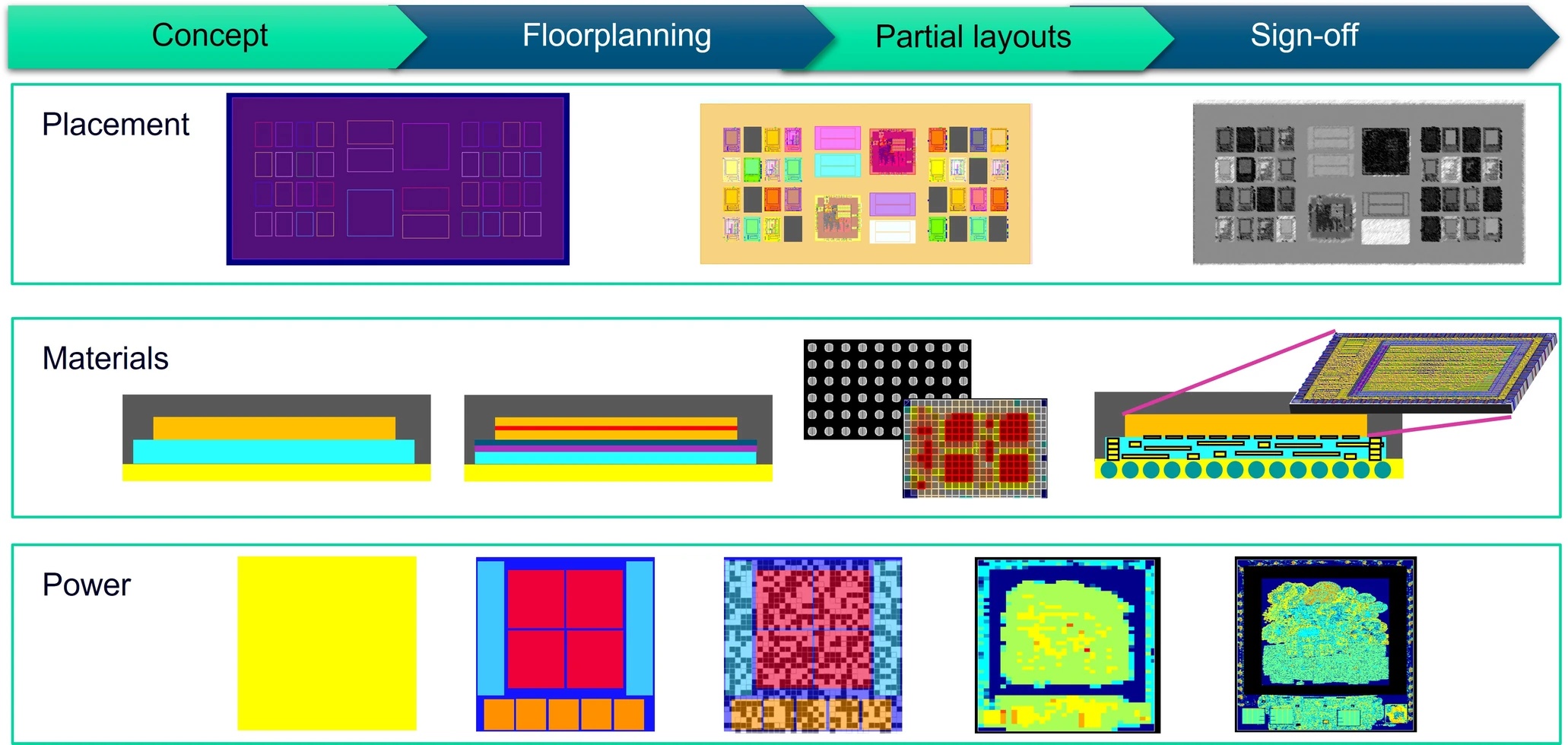

左移设计与自动化多物理场分析:实现早期预判,加速设计收敛

左移是行业通用设计理念,主张将分析与决策环节提前至设计流程中尽可能早的阶段。对 3D IC 而言,这意味着在因突发问题危及上市时间之前,就开展 “假设分析”、仿真功耗与热应力、优化布局方案。Calibre 3DStress 等现代工具可在小芯片、封装与器件定义的最早阶段开展多物理场分析。这种左移式分析能让团队在修改成本低、难度小的阶段发现问题,优化布局或材料选择。

图 3:左移设计思路在概念阶段就启动多物理场仿真。

西门子 EDA通过集成化流程自动化满足这一需求。Calibre 解决方案可实现精细的 GDSII 级分析,提取金属线、氧化层与晶体管数据,并结合 Simcenter Flotherm 进行热仿真。这种方案无需每位设计人员都成为热学或机械专家,自动化流程可一键输出结果,在常用的版图与工具中直观呈现热点、应力区域与时序影响。这类自动化多物理场工作流兼顾扩展性与效率,设计人员可在现有工具环境与流程中便捷获取深度分析结果,无需打乱现有流程或拖慢设计进度。

这些工作流能帮助 IC 设计人员理解封装、小芯片与系统层级的相互影响,无需成为多物理场专家。早期预判能让团队在器件布局、对准与材料选择上更具灵活性与信心,从源头避免失效模式或电路性能劣化。此外,结合精细的 GDSII 级分析与 Simcenter Flotherm,工作流可真实反映工艺温度、材料堆叠与装配步骤,输出结果能精准匹配器件实际表现。

适配3D复杂度的工具链升级

设计挑战不断增加,对工具链的要求也同步提升。设计人员除完成传统 2D 验证(布局布线、时序检查、设计规则检查 DRC、版图电路图一致性检查 LVS)外,还需针对集成后的封装开展新增分析。

第一代 Calibre 3D 工具聚焦于签核验证,以及不同代工厂多层、多工艺小芯片的层映射。层映射、接口检测与物理连接识别,是避免三维空间设计错误的关键。IEEE 3Dblox 等扩展标准现已支持更完善的集成化流程,可实现 DRC、LVS、PERC 分析、热仿真与应力检查。其核心目标清晰明确:实现所有层与元器件的全局可视性,让仿真结果从裸片级顺畅传递至基板与板级。

如今的综合模型不仅能覆盖翘曲、热热点等全局效应,还能捕捉应力区域导致晶体管性能偏移、影响时序收敛等器件级影响。这意味着建模不再局限于物理形变,还能直接关联器件级时序。此外,扩展标准与集成化流程可让分析结果从裸片级一直传递至封装与板级仿真,为所有参与方提供一致的数据与上下文,显著提升团队协作效率。这种迭代流程至关重要,因为热量、电迁移、电压降与机械形变都会影响寄生参数乃至单个晶体管的电气特性,初始分析的电气完整性不再成立,必须在所有相互作用的物理效应间持续迭代,才能精准核算最终电气性能。

数字孪生、AI与3D IC设计的未来

展望未来,3D IC 签核标准将愈发依赖多领域专业能力,机械、热学、功耗与时序,所有能力都将整合在易用的自动化流程中。完整的数字孪生理念可让裸片级仿真结果在全设计流程中传递,支撑严格的多物理场验证,提升可靠性。

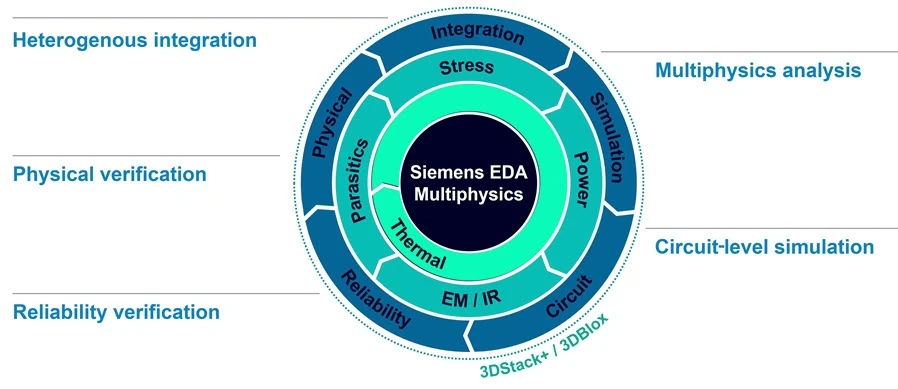

为降低这些先进技术的学习门槛,西门子 EDA 正为平台引入 AI 与智能代理功能,帮助用户快速上手。团队还在探索机器学习方法,以实现更智能的分析、更快的设计周期与更优的易用性,让设计人员聚焦创新,而非深陷复杂度泥潭。图 4 展示了西门子 EDA 的 3D IC 多物理场工作流。

图 4:西门子 EDA 完整 3D IC 多物理场工作流。

3D IC 设计的新兴方向包括采用光子技术实现高效信号传输、使用玻璃与陶瓷材料优化热缓冲,乃至芯片级液冷方案。每一项技术突破都印证着行业对更高性能、更高效率的不懈追求,而自动化、集成化的设计流程是未来设计成功的核心支撑。这种从早期版图规划(对 3D IC 而言更适合称为 “多层级规划”)启动的持续迭代流程,能让设计人员在初期数据有限的情况下做出合理决策。随着设计逐步成熟,材料特性与功耗分布数据更精准后,还可进一步优化调整,例如增设铜柱降低热影响、修改伪填充结构改善机械应力。这种主动迭代的设计思路,是实现高良率、高可靠性且电气性能最优的 3D IC 设计的关键。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。