长电科技CEO郑力:原子级先进封装定义芯片成品制造新范式

3月25日,长电科技董事、首席执行长,SEMI全球董事郑力出席在上海举办的全球规模最大、规格最高的半导体盛会——SEMICON China 2026,并在开幕论坛发表主题演讲《先进封装的原子级革新定义芯片成品制造新范式》。

郑力表示,当前先进封装走到原子级的“精度革命”,为集成电路产业带来了重要转折,产业重心正从单纯依赖晶体管微缩,扩展到强调“系统级集成、互连效率与整体能效”的范式升级。

精度革命带来范式转变

先进逻辑制程正逼近更严峻的物理与经济约束,单纯依赖传统微缩路径提升系统性能的难度显著增加。在这一背景下,混合键合等先进封装技术的发展,使芯片成品制造真正走上了系统化集成之路。

郑力表示,以混合键合为代表的原子级封装,正用一场“精度革命”来实现芯片的系统级制造。原子级封装带来了“对准精度”“互连密度”“表面粗糙度”和“界面间隙”四个“精度革命”,本质上实现了三个数量级的跨越,从而共同推高了系统性能的上限。例如,以混合键合为代表的高密度互连技术,正在把芯粒间互连从百级/千级每平方毫米推进到万级乃至更高水平。

精度的革命,对整个集成电路芯片的生产制造带来了范式的革命,从追求在单位面积上把这个晶体管做的越来越小,转向如何把芯片从系统层面做的质量更好——更短路径、更低损耗、更强信号完整性、更高可制造性与良率稳定性。诚然,生产工艺的向前发展也离不开设备、材料等整个产业生态的支撑。

与AI双向赋能

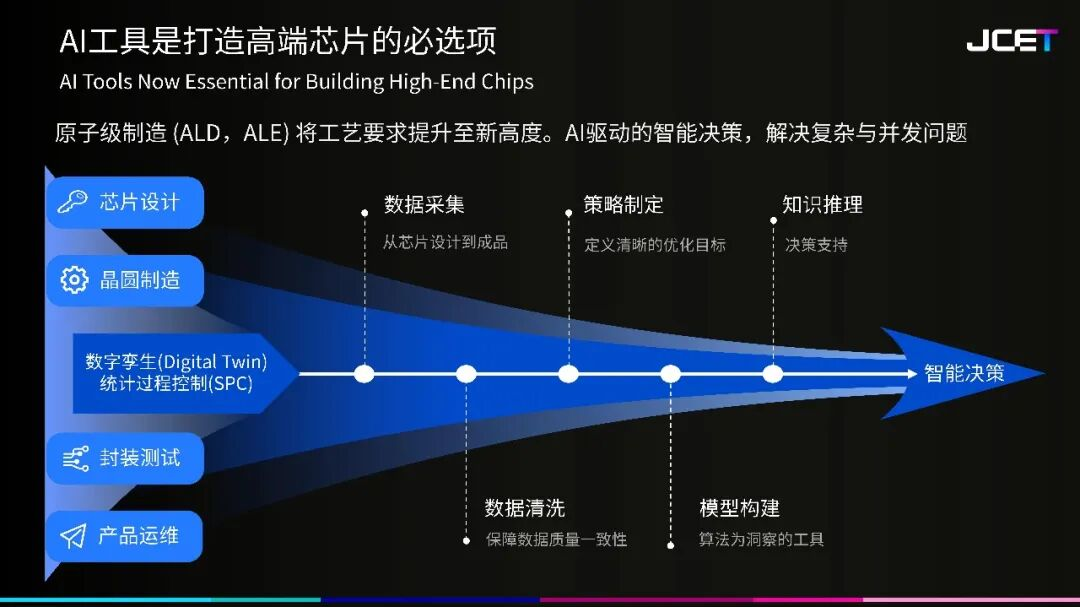

原子级封装把工艺要求抬升到新高度,复杂与并发问题显著增加,人工智能(AI)工具的应用也因此从“可选项”变为“必选项”。通过数字孪生等方法,结合数据采集、清洗、策略制定、模型构建与知识推理,AI驱动的智能决策,已广泛应用于芯片制造的良率控制、工艺精度优化,并支撑跨学科的协同仿真,把问题前移解决。

与此同时,原子级封装技术也为AI系统能力的扩展提供支撑。例如依托原子级封装,实现数千甚至数万个AI芯片的超大规模互联,从而打破算力瓶颈。依托光电合封(CPO)技术,可实现光电器件与芯片的微系统集成,为下一代高性能计算系统提供了更高效的实现路径。

此外,先进封装走向规模化的关键约束之一是测试。3D堆叠会带来复合良率、热管理、机械应力等多重挑战,因此多维度性能验证(电学、热学、机械)成为保障可靠性与良率稳定的关键环节。

未来展望

郑力表示:“站在产业发展的节点上,我们已清晰地看到,原本认为即将走向物理极限的产业难题,在微系统集成的领域上依托原子级先进封装创新,开辟出一个新的广阔天地。毫无疑问,这将为整个产业链带来丰富的发展机遇。”

原子级封装将成为后摩尔时代延续产业演进的核心路径,也是AI算力革命的重要支撑。它将以精度、互连与集成的系统性突破,重构芯片设计与制造逻辑,并推动产业迈向以系统级集成与扩展为特征的新生态。

“先进封装,芯连万象——长电科技希望与行业伙伴更紧密地结合在一起,用我们的技术革新赋能千行百业,共同开拓集成电路产业更加美好的明天。”

此内容为平台原创,著作权归平台所有。未经允许不得转载,如需转载请联系平台。