氮化镓混合结构、HEMT与衬底选择

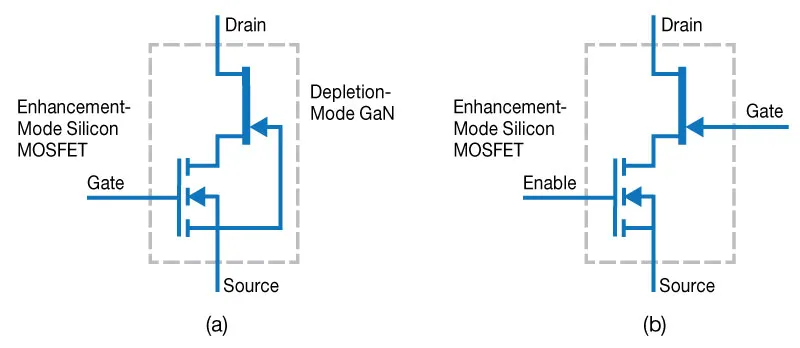

单片增强型 GaN 晶体管的一种替代方案是混合级联结构:将低压增强型硅 MOSFET 与高压耗尽型 GaN HEMT 串联。

其中,级联结构是一种务实的过渡方案:将低压增强型硅 MOSFET 与高压耗尽型 GaN HEMT 串联。MOSFET 的栅极为外部控制端;导通时,GaN 栅源电压被拉至接近零,HEMT 导通;MOSFET 关断时,GaN 栅极通过 MOSFET 获得负偏压,使高电子迁移率晶体管(HEMT)关断,在系统层面实现常关型特性。

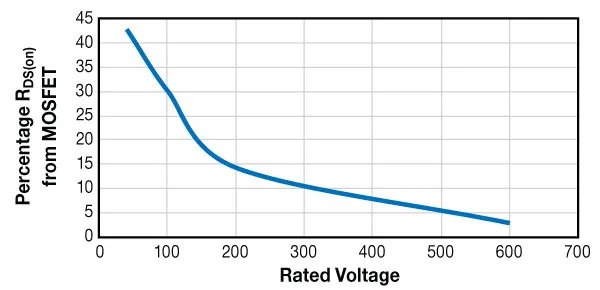

随之而来的问题是:硅 MOSFET 会给 GaN 器件带来多少额外的导通电阻 RDS(on)。级联系统中,MOSFET 对总 RDS(on) 的贡献比例与系统额定电压的关系曲线。在高压区间,GaN 器件占主导,MOSFET 的贡献很小。

由图可见,600V 级联器件因低压 MOSFET 仅增加约 3% 的 RDS(on),因为在该高压下 GaN HEMT 的漂移电阻占主导。而在低压区间,随着击穿电压 VBR 降低,GaN 器件电阻快速下降,MOSFET 的贡献愈发显著。因此,级联方案在高压(约 200V 以上)场景实用且具有吸引力;而在 100–150V 区间,通常更适合采用单片增强型 GaN。

直驱(使能)拓扑将耗尽型 GaN 栅极直接接外部驱动器(通常 0V 导通、-12~-14V 关断)。硅 MOSFET 作为安全 “使能” 开关,连接至栅极驱动器的欠压锁定(UVLO)电路。正常工作时,该硅器件保持导通、不参与开关动作;仅在电源故障时阻断 GaN 栅极。该结构可精确控制 GaN 动态特性,但需要双极性驱动能力。

HEMT晶体管的反向导通

增强型 GaN HEMT 的一个显著优势是反向导通特性。当器件名义上处于关断状态,电流从源极流向漏极时,源极电位相对栅极升高。

这一过程持续到栅极下方区域满足形成 2DEG 的阈值条件,沟道重新构建并实现反向导通。与依赖少子注入和存储的硅 MOSFET 体二极管不同,GaN 是多子导电机理,因此不存在少子存储效应,也就没有反向恢复损耗。

正向导通时,正栅压建立 2DEG 沟道,电流从漏极流向源极。在同步整流死区时间内发生反向导通时,只要漏极电压比栅极至少低一个阈值电压,电流便从源极流向漏极。

此时导通由沟道电阻决定,器件表现类似低压降二极管。与因电荷存储效应存在反向恢复损耗的硅 MOSFET 不同,一旦反向偏置消失,电流几乎立即停止。

垂直 GaN 与衬底选择

垂直 GaN 晶体管不采用横向 2DEG 输运,而是使用垂直于晶圆表面的导电通路。典型结构中,与源极相连的 p-GaN 区域从表面向漏极延伸,漏极接触位于厚层 n-GaN 漂移区底部。施加负栅压时,栅极下方 p 区之间的 n-GaN 被耗尽,阻止电流流通。

栅极正偏时,耗尽区消失,电子从源极垂直流向漏极。该架构可支持1000V 以上击穿电压并保持快速开关,有能力与高压 SiC 器件竞争。650V 以下市场由横向 GaN 主导,主要因为硅衬底成本更低、扩展性更强。

标准 200mm 硅片成本仅每片几十美元,可直接复用成熟 CMOS 产线与大规模制造工艺,还能单片集成传感电路与驱动器。与之相对,用于垂直器件的体 GaN 衬底仍局限于小尺寸(通常≤150mm),单价数百至超千美元,每平方厘米成本数十美元,严重限制了其在中压市场的成本竞争力。

从性能上看,横向 GaN HEMT 可形成高密度 2DEG,带来极高电子迁移率与低沟道电阻,从而实现优异的轻载效率与高频工作能力,是 DC-DC 转换器、服务器电源、通信、消费快充等应用的关键。

目前由 SiC MOSFET 主导的垂直架构,仍是 900V 以上高压场景的首选方案,因其在强电场下具备更高鲁棒性,且阻断电压与器件横向尺寸解耦。SiC 与未来垂直 GaN 面向高压应用,而横向 GaN 在该电压区间侧重性价比优化,巩固其中压市场的领先地位。

GaN HEMT 晶体管的制造

GaN HEMT 的制造始于在异质衬底上外延生长 GaN/AlGaN 异质结。与有源层与衬底一致的硅器件不同,GaN HEMT 需要异质外延:在晶格常数与热膨胀系数不匹配的衬底上生长纤锌矿晶体。

主流衬底材料有四种:bulk GaN、蓝宝石(Al₂O₃)、碳化硅(SiC)、硅(Si)。各自在晶格失配、热膨胀系数、热导率与成本上存在取舍。硅(111)衬底凭借低成本(200mm 晶圆每片 1–2 美元)与现有 CMOS 工艺兼容,成为商业化主力,尽管存在 17% 的晶格失配(GaN:3.189 Å,Si:3.84 Å)与 3×10⁻⁶ K⁻¹ 的热膨胀差异。

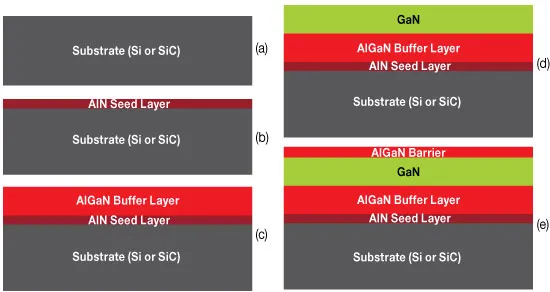

异质外延即在不同衬底上生长晶体。采用金属有机化学气相沉积(MOCVD) 生长 GaN/AlGaN 层:衬底上生长 AlN 成核层,启动晶核形成;生长 AlGaN 缓冲层,实现向纯 GaN 晶体结构的过渡;生长厚层 GaN 形成半绝缘基底;最后生长薄层 AlGaN 势垒层,通过应变形成 2DEG 导电沟道。

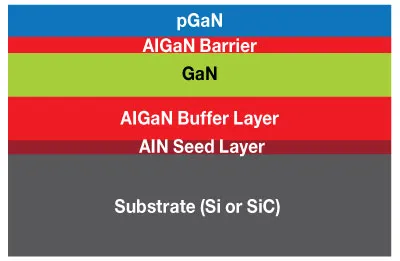

下图展示了从衬底到 2DEG 界面的完整外延堆叠。增强型器件会在 AlGaN 势垒上再生长 p-GaN 帽层,引入正电荷,使零栅压下 2DEG 被耗尽。该结构实现平行于表面的横向电子输运,这也是 GaN HEMT 与垂直硅 MOSFET 的核心区别。

欧姆接触与金属化

源极与漏极电极必须穿透 AlGaN 势垒,与 2DEG 形成低阻欧姆接触。通过多层金属与高温退火实现可靠连接。栅电极位于 AlGaN(或 p-GaN)之上,通过电场调制沟道。

后段工艺引入多层铜互连与钨通孔,将栅宽扩展至数千个并联单元。最终钝化层(SiNₓ)保护表面并调控电场,防止提前击穿。

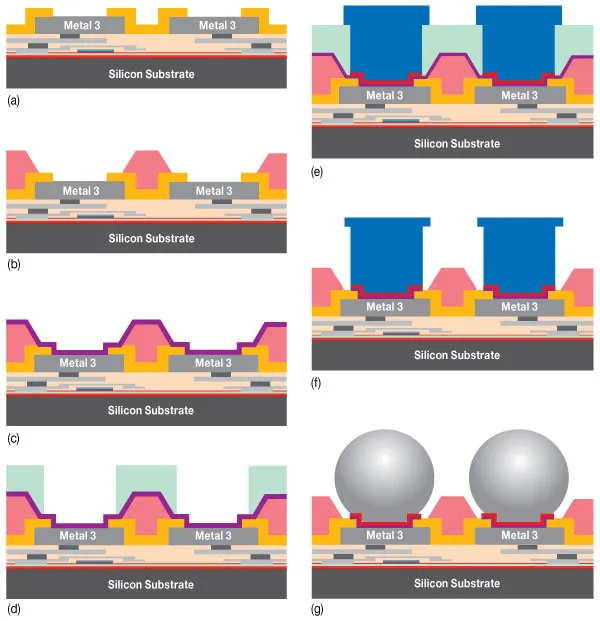

芯片级封装(BGA、LGA) 可最小化寄生参数,支持兆赫兹级开关且振铃极小。近期 QFN(无引线四方扁平封装)的进步提供了在寄生电感、电阻与导热性上几乎无妥协的替代方案。

无论是芯片级还是 QFN 封装,横向导电结构均可实现底面散热与超低电感封装。BGA 采用锡银铜微凸点(间距 150µm),用于 100–650V 器件(尺寸 1.5×1.0mm²);LGA(3.9×2.6mm²)可支持 100V 半桥、10A 连续工作。封装环路电感可降至 0.2nH 以下,支持 且无明显振铃,这在传统引线键合分立封装中无法实现。

单片集成之路

GaN HEMT 的横向结构(电流平行于表面流动),省去了深垂直通孔或沟槽工艺,实现前所未有的单片集成度。与垂直硅或 SiC 器件不同,多个无源器件、信号级晶体管与无源元件可集成在同一外延平面,互连则在上层金属层实现。这使得在比一粒米还小的单颗裸片上集成完整功率级成为可能。

GaN 单片功率级消除了分立方案中困扰系统的互连寄生。无键合线:封装电感 <0.2nH,而分立多芯片 QFN 为 1–5nH;无公共源极与栅极环路电感;引脚数大幅减少:外部连接比分立半桥 + 驱动方案少 99%。

与硅 DrMOS(驱动 + MOSFET)相比,GaN 集成可实现栅极电荷 QG 降低 10 倍 → 兆赫兹开关无显著栅损耗;反向恢复电荷 QRR=0 → 同步整流无反向恢复;裸片面积缩小 25 倍 → 同等性能下成本更低。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。