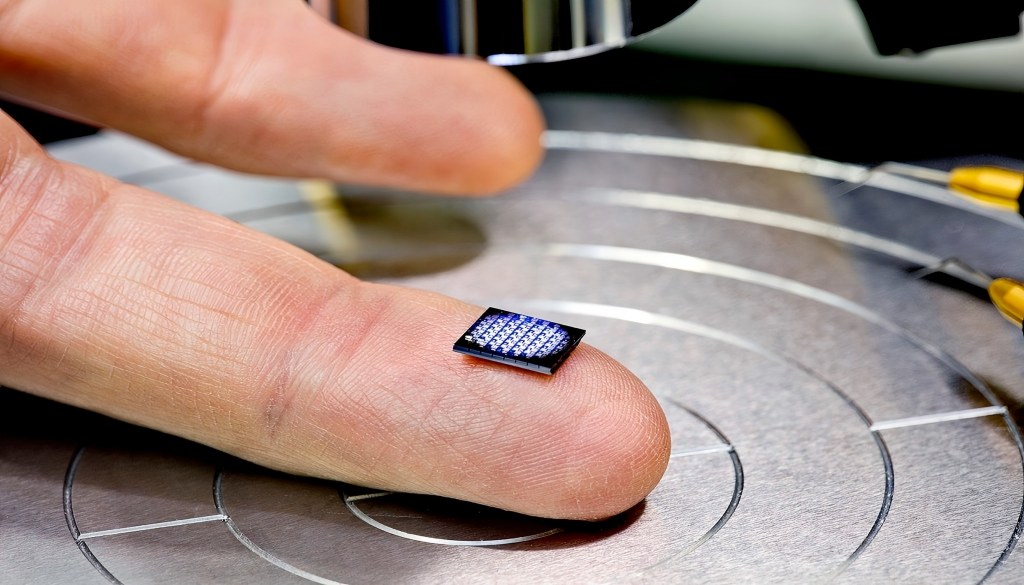

小芯片,设计之道

如今,大多数单片式 SoC 的设计都遵循一套成熟流程。先完成需求定义,再开展架构设计。随后,设计团队筛选并完成所需 IP 核的验证,将其整合进架构中,并进行芯片版图布局规划。功能验证以及早期功耗与时序预估也可在此阶段启动。团队此时便可开始 RTL 综合、初步布局,以及至少是基础的布线工作。这些任务完成后,多数 SoC 设计团队会引入物理设计专家,完成后续工作直至设计签核。

但基于小芯片(chiplet)的多裸片设计又会如何?乍看之下,任务流程与单片式 SoC 几乎一致 —— 不就是把 IP 核换成小芯片、把芯片物理设计换成中介层设计吗?

实则不然。基于小芯片的设计中,各类问题与对应工作内容,和主流单片芯片设计流程存在显著差异。除非企业计划内部培养大量专业的多裸片设计团队,否则这些问题决定了:从项目初期就引入合作伙伴至关重要。该合作伙伴需兼具小芯片与中介层设计经验,同时在全球多裸片供应链中拥有深厚资源。

小芯片设计之路

两种设计方案在项目初期就已出现分歧。从概念上看,小芯片选型与 IP 选型颇为相似。但 IP 市场已然成熟:绝大多数通用 IP 功能都有成熟供应商,专业 IP 厂商也几乎可承接各类定制需求。并且 IP 通常具备高度可配置性,既可通过 RTL 生成器设置参数,也可与供应商协同定制。

只有当 SoC 需求涉及独特功能或特殊工作条件(如行业顶尖性能、极低功耗)时,设计团队才会考虑自研 IP。

与之相反,小芯片市场虽在增长,但仍不成熟。部分功能组合尚无可用方案。而且小芯片本质是已流片完成的裸片,灵活性远不如 RTL 生成工具。你或许能找到 I/O 类型匹配的 I/O 集线器小芯片,却未必能找到配置、功耗或焊盘布局完全适配你设计的型号。

正因如此,基于小芯片的设计往往需要自研一颗或多颗小芯片,而小芯片的设计约束与独立集成电路截然不同。它们并非缩小版的 SoC。小芯片通常具备极高 I/O 密度,高速驱动器或串行收发器需适配中介层上极短的互联线路,同时焊盘布局需严格遵循中介层版图要求。

此外,由于成品模块测试时,测试设备对裸片的访问有限,小芯片对内置自测试(BiST)的重视程度通常高于传统芯片。从项目伊始就与熟悉这些问题的设计伙伴合作,可节省大量时间与精力。

存储器同样存在挑战

在小芯片设计中,有一类裸片值得特别关注:存储器。在 AI 无处不在的时代,许多小芯片架构都会集成高带宽存储器(HBM)。数据中心处理器无疑如此,而视觉处理、机器人等边缘 AI 应用也正朝着这一方向发展。

遗憾的是,HBM 接口设计、中介层布局、布线以及热分析,均与逻辑小芯片面临的挑战差异显著。HBM 不同代际标准的要求各不相同,不同供应商之间也存在差异。在供应竞争激烈的背景下,在敲定中介层设计前,确保 HBM 裸片或裸片堆叠的稳定供应至关重要。

拥有深厚 HBM 设计经验与强大供应链资源的合作伙伴,能保证你的设计实现所需存储带宽,同时采用可稳定供货的 HBM 裸片,避免中介层设计返工。

中介层设计

接下来谈谈中介层。从概念上看,中介层设计与 SoC 上的 IP 布局布线并无太大区别。但实际操作中,我们是在硅片上放置物理裸片,且各裸片的物理焊盘无法移动。因此,实际设计约束与分析工具均与芯片设计不同。

此外,此阶段的决策会影响设计流程的前后环节。小芯片间有限的带宽,可能影响架构在各裸片上的划分方式。即便空间布局问题,例如处理器小芯片与 HBM 堆叠的距离远近,也会影响架构划分与小芯片设计。

中介层设计还包含多数芯片设计团队不熟悉的工作,例如信号与电源完整性分析、3D 电磁场建模、3D 结构热学与力学分析。同时,可测试性设计也成为关键问题。成品的测试方案需合理实现所需覆盖率,且符合装配功耗预算,还会影响封装测试厂(OSAT)的选择。

最后,封装需专门设计,而非直接选用现成方案,这又需要另一套工具与分析流程。封装方案的选择会波及整个供应链:中介层设计、材料供应、具备相关能力的 OSAT 工厂地理位置等,均会受其影响。

设计需要一体化平台

将小芯片设计推向全球市场所需的工作范围与专业技能,远多于普通 SoC 设计。加之多项工作在设计流程中前后关联,进一步增加了项目复杂度。若参与的专业团队过多,沟通与变更管理将变得极为棘手。

最佳方案既非闭门造车,也非仓促拼凑一众顶尖专业顾问,更不必将全部挑战交给灵活性有限的大型代工厂。最优解可能是采用一体化整合平台。该平台整合了丰富的 IP 资源、小芯片设计经验、中介层专业能力、HBM 供应商,以及全球多家中介层代工厂和支持晶圆级芯片封装的 OSAT 厂商。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。