3D晶体管,新突破

韩国大邱庆北科学技术院电子电气与计算机科学系张在恩教授与表高恩博士领衔的研究团队,在全球范围内首次成功研发出 “双调控垂直堆叠晶体管”。该器件即使在二维纳米级沟道结构中,也能稳定运行且无电流泄漏,为后摩尔时代半导体产业突破物理极限提供了关键技术支撑。当前,全球 AI、5G 通信、物联网等新兴技术的爆发式增长,对芯片的集成度、能效比和响应速度提出了前所未有的严苛要求,传统平面晶体管及 FinFET 架构已逐渐逼近物理性能天花板,3D 堆叠技术成为行业公认的下一代核心发展方向,此次 DGIST 的研究成果恰好精准击中了产业升级的核心痛点。

近年来,半导体行业遵循 “摩尔定律” 持续推进制程微缩,追求在有限芯片空间内集成更多晶体管,但这一发展路径已逐渐逼近物理极限与量子隧穿效应的双重制约。当 CMOS 工艺演进至 3nm 及以下先进节点时,短沟道效应、栅极漏电、掺杂控制精度不足等问题日益凸显,不仅导致器件性能提升放缓,还使芯片功耗和制造成本急剧增加。为突破这一瓶颈,将导电沟道垂直层叠的“垂直堆叠晶体管”凭借其超高集成潜力、灵活的栅长设计及空间利用率优势,被全球半导体企业和科研机构视为下一代 3D 半导体最具可行性的技术方向。

然而,传统垂直堆叠晶体管长期存在一个致命缺陷:受限于单一栅极或非对称电极结构,栅极电信号无法均匀穿透至沟道内部,导致沟道长度缩短到纳米级别时,极易出现电流泄漏、开关特性退化或器件工作不稳定等问题,这一技术瓶颈严重制约了 3D 堆叠半导体的商业化落地进程。

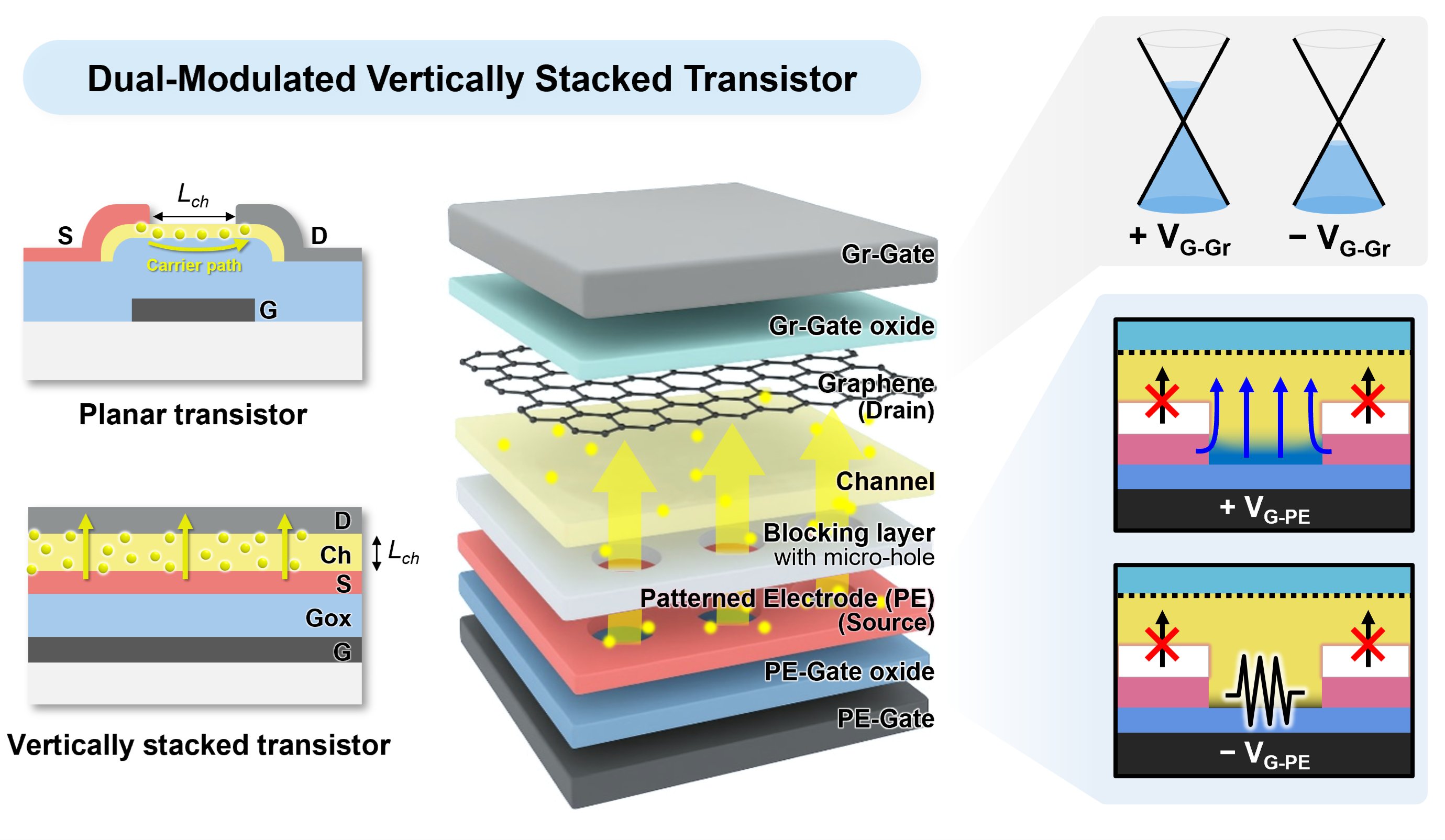

为彻底解决传统垂直堆叠晶体管的核心痛点,DGIST 研究团队经过长期技术攻关,创新性地提出了“双调控结构”设计方案:在沟道上方和下方分别设置两个功能互补的栅极,通过协同作用实现对沟道电流的精准控制。这一设计颠覆了传统垂直晶体管的单栅极控制模式,使电流以“三明治式”形态在上下电极与沟道之间流通,上下电极隔着沟道相对分布,形成全方位、无死角的栅极控制场,从根本上解决了信号传递不均的问题。

在具体技术实现层面,研究团队采用了多项创新设计:首先,在下电极上精准制作微型开孔结构,使栅极电信号能够穿透电极层,更深入地传递至沟道内部,确保沟道全域都能受到均匀的电场调控;其次,上电极选用了新型二维材料石墨烯,利用其超高导电性、优异的栅控特性和原子级平整的表面形貌,实现对电流的高精度、快速响应控制,这一材料选择与普渡大学、麻省理工学院等机构在 2D 半导体器件领域的前沿研究形成技术呼应,印证了石墨烯在先进晶体管中的应用潜力;同时,团队在器件易发生漏电的界面区域专门集成了高性能阻挡层,通过材料选型与结构优化,从根本上切断了无效功耗的漏电通路,构建起稳定可靠的器件工作架构。

经过系统的测试验证,该团队研发的 “双调控垂直堆叠晶体管” 展现出多项行业领先的性能指标:其一,成功实现了纳米级超薄平面导电层,其厚度远小于人类发丝直径,达到二维材料器件的先进水平,为器件的高密度堆叠奠定了基础;其二,漏电流控制能力突出,可将断电状态下的微小漏电流抑制到10⁻¹² 安培的极低水平,这一数值较传统垂直晶体管提升了 1-2 个数量级,有效降低了器件的静态功耗,符合下一代低功耗电子设备的发展需求;其三,开关特性优异,开关状态区分清晰,开关比达到工业应用标准,为逻辑器件的稳定工作提供了核心保障;其四,低电压适应性强,即使在低供电电压下也能输出足够的驱动电流,进一步降低了器件运行功耗;其五,环境适应性好,在光照、高低温循环、长时间连续运行等严苛条件下仍能保持稳定工作,展现出良好的工业应用潜力和可靠性。

尤为值得关注的是,该技术在制造工艺上具备显著的产业化优势 ——无需昂贵的超高精度对准工艺与高温制程。传统 3D 堆叠器件往往依赖复杂的超精密光刻对准技术和高温退火工艺,不仅大幅增加了生产成本,还降低了生产良率,限制了其大规模应用。而 DGIST 研发的这一技术路径,通过结构创新简化了制造流程,降低了对设备精度和工艺条件的要求,在大面积、多层堆叠结构的规模化生产中具备独特竞争力,为高集成度 3D 半导体的低成本制造提供了可行方案,有望加速相关产品的商业化落地进程。

从应用前景来看,该技术的突破将产生广泛而深远的产业影响,未来有望在多个工业领域实现重大技术突破:在高集成度 3D 半导体领域,可助力芯片设计企业实现更高密度的晶体管集成,满足 AI 芯片、高性能计算(HPC)芯片对集成度和算力的极致需求,为大模型训练、量子计算等算力密集型应用提供硬件支撑;在下一代低功耗逻辑器件领域,其优异的漏电流控制能力和低电压工作特性,可有效延长智能手机、笔记本电脑、物联网终端等移动设备的续航时间,推动消费电子设备向更轻薄、长续航方向发展;在存储技术领域,有望与 3D NAND、MRAM 等新型存储技术结合,研发出兼具高速读写、高可靠性和低功耗特性的存储器件,解决存储与计算之间的性能鸿沟,推动 “存算一体” 架构的发展;在柔性电子领域,其温和的制造工艺与稳定的工作特性,完美适配了柔性基底的加工要求,为可穿戴设备、柔性显示屏、柔性传感器等新兴产品的技术升级提供核心支持,拓展半导体技术的应用边界。

DGIST 电子电气与计算机科学系张在恩教授表示:“本研究提出了全新的双栅极设计方案,可让纳米级沟道实现稳定工作。该技术突破了传统垂直晶体管的核心局限,有望成为加速下一代低功耗、高集成度 3D 半导体时代到来的关键解决方案。” 这一评价得到了行业专家的广泛认同,业内普遍认为,该研究为 3D 堆叠半导体技术提供了新的设计思路和技术路径,其创新的双调控结构和简化的制造工艺,可能会推动整个半导体行业的技术路线调整,引发相关领域的研发热潮。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。