HBM4性能跃升,SK海力士祭出封装新方案

SK海力士正试图对高带宽内存(HBM)所用封装技术进行变革。据悉,该公司已研发出能够在不进行大规模工艺转换的前提下,强化HBM稳定性与性能的技术,目前正在验证阶段。若该技术最终实现商用,不仅有望满足英伟达对HBM4的最高性能要求,也将让下一代产品的性能提升变得更加容易。业内正高度关注这项技术的成败。

HBM4已启动初期量产,提前备货应对英伟达认证

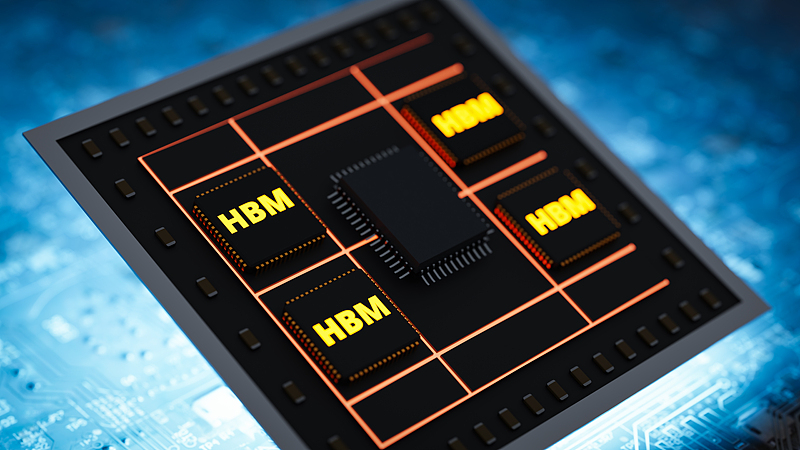

HBM 是将多颗 DRAM 垂直堆叠,通过硅通孔(TSV)实现连接的内存。各层 DRAM 通过微小凸起的微凸块(Micro Bump)进行键合。HBM4将从 12 层堆叠产品开始商用。

SK海力士目前已启动 HBM4初期量产。由于HBM4的交付周期(量产+供货所需总时间)约为 6 个月,此举意在英伟达正式质量认证完成前,提前进行产品量产。

HBM4供货基本无虞,但冲击最高性能仍存挑战

此前,业内一直担忧SK海力士HBM4的性能与稳定性出现下滑。原因在于,英伟达要求HBM4的最高性能(单引脚速率)从原本标准的 8Gbps 大幅提升至11.7Gbps,开发难度急剧上升。

事实上,SK海力士HBM4在与 AI 加速器整合的 2.5D 封装测试过程中,一度难以达到最高性能,直至今年初仍在对部分电路进行改进。受此影响,大规模量产上量时点也晚于业界此前预期。

不过综合业内消息,目前SK海力士面向英伟达的HBM4供货出现重大中断的可能性极低。主要原因在于供应链格局。尽管英伟达对HBM4提出高规格要求,但如果坚持高标准,可能会限制今年下半年最新 AI 加速器 “Rubin” 的充足供货。即使是目前在HBM4上反馈最好的三星电子,考虑到良率、1c 级 DRAM 投资状况等因素,短期内也难以快速扩大供应量。

因此业内认为,英伟达很有可能将初期供货的HBM4性能要求放宽至 10Gbps 级别。

半导体专业分析机构 SemiAnalysis 在近期报告中指出:“英伟达最初将 Rubin 芯片的总带宽目标定为 22TB/s,但内存厂商难以满足其要求。预计初期出货量将接近更低的 20TB/s(折算后HBM4单引脚速率约 10Gbps 级别)。”

一位半导体业内人士表示:“HBM 供应链不能只看速度,还必须综合考虑良率、供应链稳定性等多重因素,因此SK海力士仍有望成为最大供货方。但在冲击最高性能的改进工作上,技术层面没有松懈空间。”

突破HBM性能极限的 “新武器”,目前处于验证阶段

与此相关,SK海力士正尝试引入目标应用于HBM4及下一代产品的全新封装工艺。

业内认为,HBM4性能受限的最大原因是I/O 端口数量扩容。I/O 是数据收发通道,HBM4的 I/O 数量较前代翻倍,达到2048 个。但 I/O 数量翻倍后,密集的端口之间可能产生干扰。同时,受电压问题影响,底层逻辑裸片难以将电力充分传输到最顶层。

尤其SK海力士,相比主要竞争对手三星电子,采用的是上一代 1b(第五代 10 纳米级)DRAM;逻辑裸片也采用台积电 12 纳米工艺,集成度低于三星。因此在技术上,更容易受到 I/O 数量增加带来的问题影响。

无需大幅改产线即可提升HBM性能与稳定性,商用前景受关注

据悉,SK海力士已通过全新封装工艺找到突破口,核心在于两点,一是提升核心裸片厚度,二是缩小 DRAM 之间的间距(Gap)

首先,将部分上层 DRAM 的厚度做得比以往更厚。以往为满足HBM4封装高度标准(775 微米),需要对 DRAM 背面进行减薄工艺。但 DRAM 过薄会导致芯片性能下降,或更容易因外部冲击受损。因此业内认为,SK海力士希望通过增加 DRAM 厚度来强化HBM4稳定性。

同时进一步缩小 DRAM 之间的间距,在不增加整体封装厚度的前提下提升电源效率。DRAM 之间距离更近,数据传输更快,传输到 DRAM 顶层所需的功耗也会降低。

关键难点在于实现难度。DRAM 间距缩小后,难以将 MUF材料稳定地注入缝隙。MUF 承担 DRAM 保护、绝缘等作用,若填充不均产生空隙(Void),可能导致芯片不良。

SK海力士已研发出可解决这一问题的新型封装技术。具体细节尚未公开,但其核心思路是:无需大规模工艺与设备变更,即可在保证良率的前提下缩小 DRAM 间距。据悉,近期内部测试结果积极。若SK海力士快速将该技术商用,预计可有效缩小HBM4及下一代产品的 DRAM 间距。当然,该技术在量产应用中仍存在不确定性。

一位知情人士表示:“SK海力士为突破现有HBM极限研发了全新封装工艺,目前正积极开展验证。由于无需大额设备投资即可改善HBM性能,一旦商用,影响力将不容小觑。”

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。