UCIe核心技术组件,现已全部就绪

随着小芯片使用率持续上升,尤其是在数据中心领域,UCIe 正式发布了 3.0 版本,延续了自 2023 年以来每年一更的节奏。该版本将数据速率提升一倍,增强了可管理性,并覆盖了此前版本难以轻松处理的三类新场景。

随着这些技术进步持续重塑行业格局,理解它们对实际应用产生的影响至关重要。

“如今,AI 数据中心工作负载对算力和带宽的需求规模,已远超传统单片裸片所能提供的极限。”Alphawave Semi 首席产品营销经理 Archana Cheruliyil 在与西门子 EDA 联合举办的网络研讨会上表示,“掩模极限、良率限制以及供电挑战,使得将这些巨型器件做成单芯片既不现实,在很多情况下甚至根本不可能。”

这意味着小芯片之间必须能够相互通信。“一些最棘手的异质集成难题,在于实现小芯片间的高效通信,以及管理布线与连接的复杂性。” 西门子 EDA 3D-IC 封装流程高级产品专家 Kendall Hiles 补充道。

UCIe与BoW是面向小芯片间连接的两大核心裸片对裸片标准。UCIe 于 2022 年推出,对小芯片互联采取全面视角,既覆盖最底层的物理信号,也包含上层适配协议。UCIe 产业联盟着眼于未来可能出现的小芯片市场,在这一场景中,互操作性将至关重要。

2024年发布的2.0版本新增了管理功能等多项内容。当时行业普遍担心这些功能过于庞大,让 UCIe 背上了 “重量级” 的名声。但当时外界并不清楚的是,其中许多功能都是可选的,开发者可自行决定实现哪些特性。

“一开始人们看到规范时会想:‘哦,这太笨重了,里面全是我用不到的功能。’” Cadence裸片间接口 IP 产品营销总监 Mayank Bhatnagar 表示,“但实际上大部分功能都是可选的。”

从那以后,这种看法逐渐缓和,对采用这一 “笨重” 标准的抵触情绪也有所减弱。3.0 版本引发的争议明显更少。

面向平面封装的带宽提升

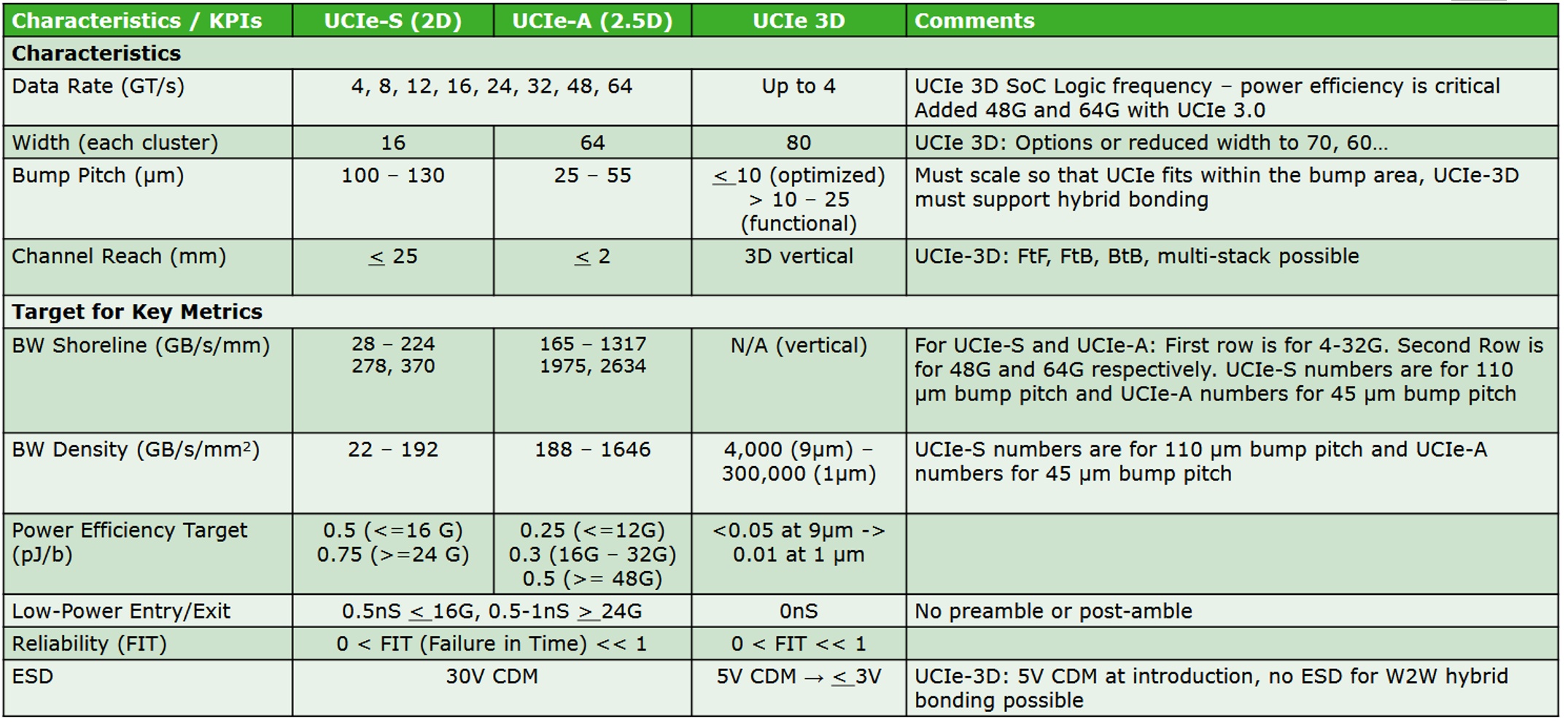

UCIe-S和UCIe-A的最大允许数据速率从 32 GT/s 提升至 64 GT/s。不过这一提升仅适用于 2D 与 2.5D 设计。标准同时也定义了 48 GT/s 这一数据速率。

“这是 UCIe 3.0 最主要的升级,也是驱动市场的关键。” 新思科技高级产品经理 Manuel Mota 表示,“并不是说之前的速率对所有应用都不够,而是行业在前进,我们也必须跟上。”

3D 封装未纳入此次速率翻倍的原因与边缘带宽(shoreline)有关。在平面设计中,信号向裸片边缘汇聚以连接相邻裸片,因此边缘带宽受限于裸片周长。

而在 3D 堆叠中,裸片并非与旁边芯片通信,而是通过硅通孔(TSV)与上下方的芯片通信。允许的 TSV 数量由裸片面积决定,而非周长。UCIe 联盟认为,仅凭面积就足以提供充足信号空间,无需翻倍数据速率。

“对于 3D 架构,我们不需要翻倍数据速率。”UCIe 联盟主席、英特尔资深院士Debendra Das Sharma表示,“事实上,我们目前的方案已经非常出色。”

单时钟、四边沿

更高的数据速率得益于四分频信令(quarter rate signaling)。该技术此前已支持 32 GT/s,但无法支持更高速率,如今已扩展至 48 GT/s 与 64 GT/s。四分频信令也可称为四倍数据速率(QDR)信令。系统从基础时钟内部生成两路双倍数据速率(DDR)时钟,二者同源但相位相差 90 度。

以 64 Gbps 为例,“时钟频率为 16 Gbps,且存在两路时钟。”Das Sharma 解释道,“一路与另一路相差 90 度。发送端将信号偏移 90 度,接收端同样偏移 90 度后捕获数据。”

这意味着两路内部时钟各有上升沿与下降沿,最终在 0、90、180、270 度四个位置形成采样边沿。

“四分频方案非常有价值,因为它显著降低了用户与厂商在开发新 IP 时面临的风险。”Bhatnagar 指出。

可靠性与功耗

不过,48 GT/s 与 64 GT/s 的误码率(BER)有所不同:48 GT/s 下为 10⁻¹⁵,64 GT/s 下为 10⁻¹²。UCIe 联盟表示,尽管两者相差三个数量级,但在具备 CRC 校验与重传机制的前提下,均处于可接受范围。

在较低速率下,功耗仍保持在 0.5 pJ/bit 以下。更高速度的设计需要增强型均衡技术,功耗会随之上升,目标指标定为 0.75 pJ/bit。

新增带宽在凸点位置与前代完全一致,因此具备完全向后兼容能力。但更高的速度也给信号完整性保障带来了更大挑战。

尽管信令、可靠性与能效方面取得进步,其对系统设计与集成的更广泛影响正日益显著。随着行业不断发展,应对这些持续变化需求的新挑战与新方案也不断涌现。

“AI 正驱动前所未有的带宽需求,裸片间连接的分析难度呈指数级增长。” 西门子 EDA 高级营销战略经理 Emily Yan 表示。

异质集成带来了新的复杂度,从不断攀升的功耗与散热需求,到堆叠架构下的全系统级验证。“随着 UCIe 向 64 Gbps 推进,设计裕量缩小、布线密度提升、信号完整性风险成倍增加,使得系统级收敛比以往任何时候都更具挑战性。” 西门子的 Hiles 说道。

更优的启动与优先级机制

UCIe 2.0 引入了可管理性,3.0 版本在此基础上进一步升级,其中一项改进针对先进封装的启动方式。

传统基于小芯片的封装,需要为每个需要启动的小芯片配备独立固件文件或加载器。新版本可将这些文件合并为单一源,统一供给所有小芯片或部分组合芯片使用。

“如果一个系统由多个小芯片构成,而每个芯片都需要独立固件,就会出现先有鸡还是先有蛋的问题:要么为每个小芯片配置独立路径加载固件,让所有芯片同时启动;要么先唤醒所有 UCIe 接口,再通过一条路径将固件分发给所有小芯片。”Mota 解释道,“UCIe 提供了一套通过主通道或边带通道分发固件的路径与方法,流程统一,无需为每个小芯片单独配置闪存链路或独立并行路径。”

在 UCIe 3.0 之前,优先级通知事件通过主通道发送,偶尔会出现重要消息被低优先级数据阻塞的情况。此外,所有经过主通道的信息都必须通过主小芯片上的信任根(RoT)校验,导致消息延迟。如今这类消息可通过边带通道传输,速度虽慢,但可用性更高,且不会受信任根校验带来的延迟影响。

“将时钟拉低八个周期,即可告知对端在下一个 8 UI(单位间隔)边界处将传输高优先级数据。”Das Sharma 表示,“该模式可持续 64 UI,之后恢复长 payload 传输。”

不过,边带通道的安全机制仍在完善中。

边带传输距离延长与新增开漏引脚

这类高速接口的信号传输距离有限,在 UCIe 中,主通道与边带通道此前限制相同。但边带工作频率远低于主通道,其距离限制显得过于严格。“此前边带通道最远只能传输 25 毫米,现在可以达到 100 毫米。”Bhatnagar 说。

“这样做的目的是让多个小芯片共享走线,实现边带通道的星型连接。”Mota 表示,“主通道传输距离保持不变,因为它是点到点连接。”

3.0 版本允许信号在单跳内传输更远距离,同时仍支持消息在小芯片之间转发。

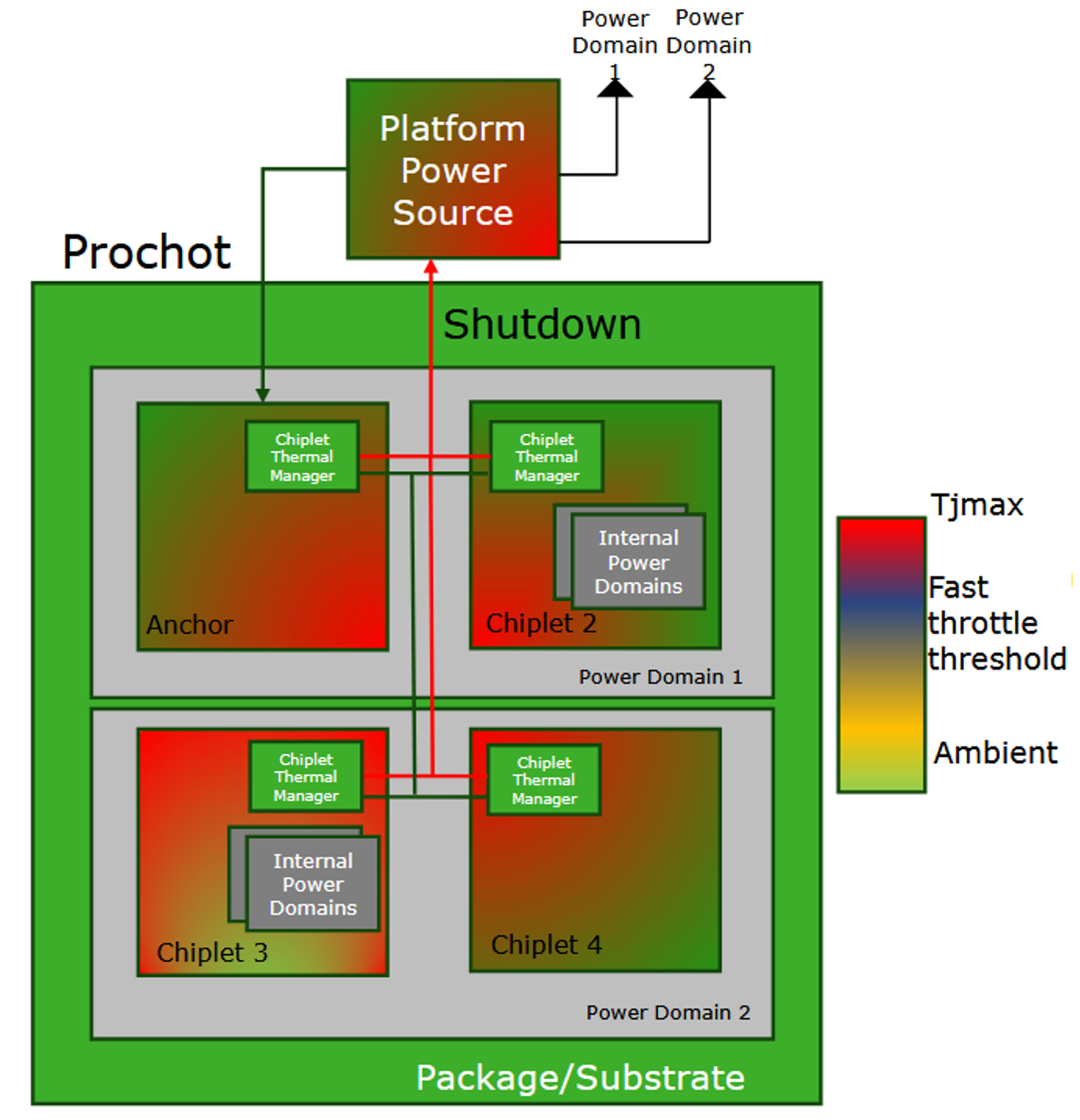

新增的两路开漏引脚可实现快速节流与紧急关断。若任意小芯片检测温度过高,一个阈值可触发降速,更高阈值则触发所有小芯片关断,避免过热损坏。

“一旦出现问题,需要快速响应。如果通过常规方式,边带或主通道传输指令,速度会太慢。”Mota 说,“开漏引脚提供了一种标准化的快速响应机制。一旦某个小芯片过热,可同时通知所有部件:‘即将进入下一状态’,所有芯片立即执行,无需经过关断协议流程。”

该功能对整体系统可靠性影响重大。“这种快速节流与紧急关断支持非常重要,从可靠性角度看,尤其适用于汽车应用。”Bhatnagar 指出。

更优的流式传输与重新校准

UCIe 3.0 覆盖了前代未解决的若干场景,其中最突出的是连续流式传输。严格来说这并非全新功能,但此前很难实现无中断传输,需要在主通道中占用带宽插入标记,且可用时钟频率有限。

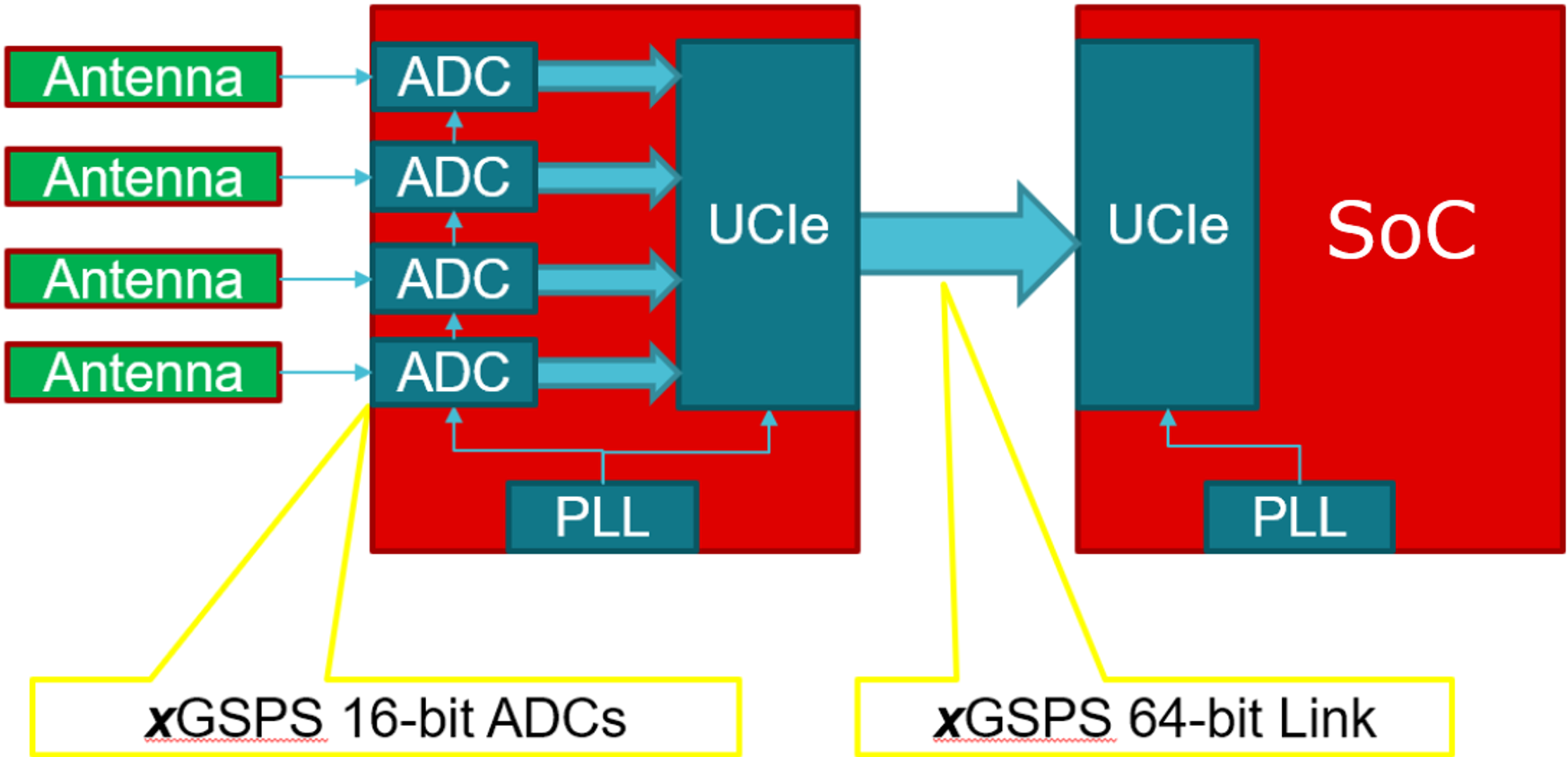

需要该功能的应用会以恒定速率产生数据,且必须以相同速率传输。天线就是典型案例:一个小芯片上生成的数字数据需要传输到另一个芯片,例如 SoC。

这类系统对时钟频率要求苛刻,设计者不希望使用可能与被采样信号产生拍频干扰的频率。此前版本中,UCIe 仅支持特定允许频率,未必符合设计者需求。通过支持频率范围选择,“设计者可使用不会与射频信道产生干扰的 UCIe 工作频率。”Mota 表示。

数据速率不再依赖 PLL 从指定时钟生成目标时钟,而是直接来自参考时钟。只需调整时钟频率即可改变数据速率。Valid 信号上的编码被复用,使得同步与校验可通过带外方式处理。

另一项新功能允许链路接收端向发送端请求重新校准。这可以减轻接收端处理随时间漂移数据的负担,同时简化初始化流程 —— 无需重新初始化即可完成校准,从而降低功耗。

“这让物理层(PHY)能够在工作状态下重新校准,从而支持更宽的环境条件范围。”Mota 指出。

更深睡眠模式与CHI协议支持

最后一类新场景针对深度睡眠模式(L2)。在 UCIe 3.0 之前,即使主通道进入睡眠,边带通道仍需保持开启。新版本新增能力:可关闭边带通道,仅保留少量电路唤醒以检测退出睡眠的信号,从而降低睡眠功耗。

“此前边带必须保持激活、保持唤醒,才能唤醒其他模块。”Das Sharma 解释道,“现在我们允许对边带大部分区域进行电源门控。”

实现按需唤醒所需的常驻电路极少。“只需两三个门电路监测电平跳变即可,甚至不需要时钟。”Das Sharma 说,“只要保持这部分供电,其余全部关断,就能实现更深层次的功耗节省。”

“现在可以直接唤醒边带通道,无需执行完整初始化流程。”Mota 表示。

最后一项进展来自 UCIe 联盟之外。联盟此前已在 UCIe 之上实现了 PCIe 与 CXL 协议。如今Arm紧随其后,在 UCIe 之上提供其广泛使用的 CHI 一致性协议。“很多厂商希望在 UCIe 上运行 AMBA 协议。”Arm 基础设施业务部营销副总裁 Eddie Ramirez 表示,“该协议支持内存与 I/O 一致性,因此受到青睐。英伟达在 Grace Blackwell 方案中通过 NVLink 运行 AMBA 协议。对比对象并非 UCIe 本身,因为它只是物理层接口,最接近的对标是业界试图用 CXL Type 2 实现的目标。”

该实现通过将 CHI 数据映射到 UCIe 格式完成。“Arm 定义了将片间 CHI 协议映射为可在 UCIe 上简易传输的微包(flit)的方法。”Mota 解释道。

这些进步共同体现了 UCIe 在能效与协议支持方面的进展。随着技术不断演进,这些更新为更广泛的采用与更多样化的应用场景铺平了道路,为未来发展奠定基础。

核心框架已基本成型

UCIe 采取了初期以最小功能集发布,再通过反馈与版本迭代补齐能力的路线。前几个版本均在初代基础上实现重大升级。而 3.0 尽管包含多项重要新功能,却无需对接口做任何改动:Valid 引脚等现有信号被复用于新功能,开漏引脚为新增引脚,而非对前代接口的修改。

尽管联盟预计将继续进行必要升级,但目前主要缺失功能与 “过于笨重” 的顾虑已基本得到解决。行业反对声音变少,进展案例越来越多。

“在 UCIe 出现之前,几乎所有厂商都使用定制方案。”Bhatnagar 表示,“就连Cadence也有名为 Ultralink 的定制方案,运行速率 40 G。当时厂商对迁移到 UCIe 持犹豫态度,担心面积、性能、速度等方面的开销。但现在 UCIe 已提升至 64 Gbps,我们相信采用率将会更高。”

BoW 仍将占据一席之地,尤其适用于需要极简接口与最低功耗的设计。“显然 BoW 依然存在,也有其支持者。”Mota 表示,“它们不一定会消失,但行业主流已转向 UCIe,或至少转向基于 UCIe 标准的方案。”

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。