突破先进工艺瓶颈:3D-IC 成半导体创新核心引擎

随着先进工艺节点的扩展日益受到成本、良率和功率密度的限制,半导体创新正果断地转向 3D集成电路 技术、芯片组和异构集成。在人工智能基础设施、云计算、汽车电子和高性能系统等领域,设计团队正超越单片SoC,通过先进的封装技术释放更高水平的性能、效率和可扩展性。

本文汇总了源自实际生产部署的Cadence 3D-IC案例研究。这些案例重点展示了带宽、能效、可靠性和流片可预测性方面的可衡量成果,证明了 Cadence 如何实现大规模、可重复的 3D-IC 流片成功。

利用 3.5D 集成技术扩展下一代 AI ASIC

在人工智能和机器学习 (ML) 加速器领域,大型语言模型 (LLM) 和深度学习推荐模型 (DLRM) 的快速发展对内存带宽和计算密度提出了前所未有的要求。为了满足这些需求,人工智能专用集成电路 (ASIC) 已从大型单芯片发展到由先进封装技术支持的异构芯片架构。

一家领先的基础设施芯片供应商代表了一种日益增长的3D集成电路实现方案,通常被称为“3.5D”集成。这种方法结合了大型光罩级逻辑芯片、2.5D中介层和选择性3D芯片堆叠,以实现架构可扩展性。虽然这些设计功能强大,但在布局规划、组装正确性和芯片间连接方面却带来了重大挑战。

借助 Cadence Integrity 3D-IC 平台,设计团队实施了一种“从设计之初就保证正确性”的布局规划和组装方法,从而在芯片和封装结构中保持了系统意图。该平台无需依赖分散的工具交接,即可实现早期堆叠规划、确定性连接定义以及贯穿整个构建过程的持续验证。

最终实现了一次性成功制造ASIC芯片——这对于大规模AI加速器至关重要,因为重新设计芯片会带来巨大的成本和进度风险。这个例子表明,Cadence 3D-IC解决方案越来越注重可预测性和制造就绪性,而不仅仅是峰值性能。

大规模芯片组设计的集成系统验证

云规模的工作负载对基于芯片组的系统架构提出了持续的压力,要求在紧迫的部署期限内实现高性能。在一家大型云平台提供商开发的先进多芯片计算平台中,模块化芯片组提高了可扩展性,但也增加了系统规划、验证和最终验收的复杂性。

传统流程中最棘手的挑战之一是,当扁平化的GDS数据传输到下游系统分析工具时,系统意图容易丢失。多边形抽象、转换错误以及验证步骤脱节常常导致错误的信号完整性(SI)和电源完整性(PI)违例,从而延长分析周期并减缓设计收敛过程。

该方法显著提高了芯片组装过程中的生产效率,并缩短了整体分析时间,从而强化了 EDA 集成在实现成功且可扩展的异构集成方面的重要性。

此次客户部署展示了 Cadence 3D-IC 设计方法如何受益于紧密集成的规划和分析。借助 Integrity 3D-IC 平台,在统一的在线设计环境中完成了多芯片构建、信号完整性 (SI) 和性能完整性 (PI) 分析。直接在构建过程中进行切割分析消除了转换误差,并使结果能够直接反向标注到物理实现中。

该方法显著提高了芯片组装过程中的生产效率,并缩短了整体分析时间,从而强化了 EDA 集成在可扩展异构集成工作流程中的重要性。

适用于先进 3D-IC 架构的可扩展电源完整性

随着3D集成电路架构复杂性的不断增加,电源分配网络(PDN)已成为一项主要的设计风险。垂直堆叠、高密度微凸块阵列和多芯片交互作用暴露了传统2D电源完整性方法的局限性,尤其是在先进节点上。

来自一家领先半导体制造商的先进封装案例研究表明,Cadence 如何通过可扩展的电源完整性分析,助力实现可量产的 3D-IC 解决方案。该设计团队利用 Voltus IC 电源完整性解决方案、 Innovus 实施系统和 Integrity 3D-IC 平台,实施了一套全面的电源完整性 (PI) 方法,涵盖从早期探索到最终验收的整个过程。

两种技术被证明效果尤为显著。自适应分区将具有相似空间特征的芯片分组,减少了不必要的仿真迭代次数,提高了收敛速度。而基于XM的分层建模实现了高精度的宏观抽象,在保持签核级精度的同时,显著缩短了EM-IR仿真周期。

在一个包含约 10 万个凸点的先进 2.5D 设计中,EM-IR 测试周期缩短了 10% 以上,而对精度的影响微乎其微。在规模更大的分层设计中,仿真时间缩短了 50% 以上,电源和接地节点数量也从数十亿减少到可控水平。这些结果凸显了 Cadence 3D-IC 设计成果越来越注重生产效率、可扩展性和可靠性,而不仅仅是性能。

面向大批量生产的代工厂级3D-IC制造流程

除了在各个客户项目中取得的成功部署之外,Cadence 的 3D-IC 生态系统实力还得益于与领先半导体代工厂的深度持续合作。通过与代工厂的紧密协作,Cadence 提供经过生产验证的 3D-IC 设计流程,这些流程经过认证、验证,并针对制造就绪性进行了专门设计,而不仅仅是设计可行性。

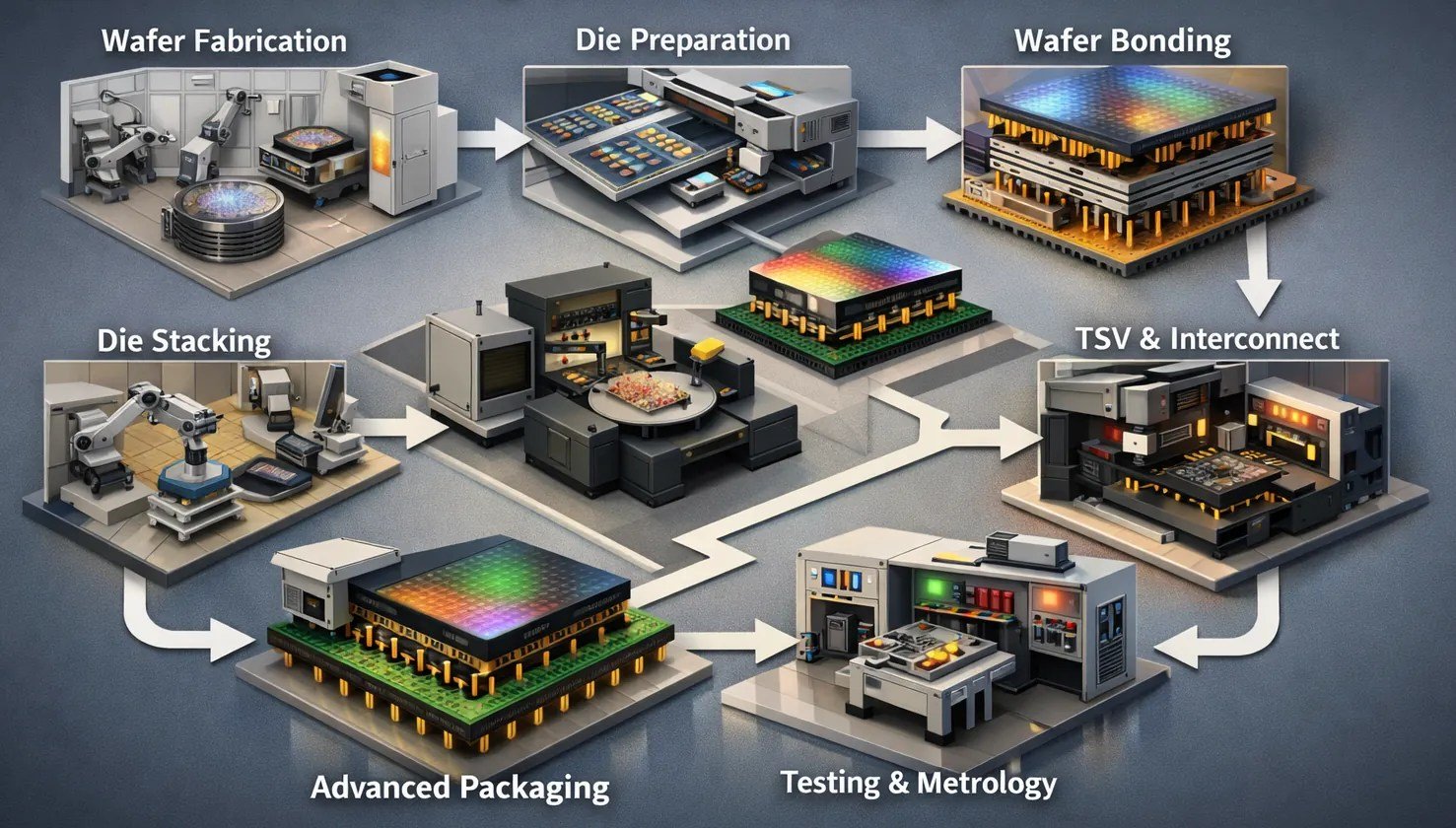

可扩展3D-IC制造工作流程的代表性可视化

Cadence 多芯片 3D-IC 解决方案 支持多种先进集成技术,包括复杂的芯片堆叠结构、混合键合、硅和有机中介层,以及新兴的代工厂专用封装创新技术。这些功能与 Clarity 3D Solver、 Sigrity X Platform、 Celsius Thermal Solver和 Voltus IC 电源完整性解决方案紧密集成,从而在整个设计周期中实现系统级的 SI、PI、热分析和可靠性分析。

通过将代工厂要求直接嵌入到 3D-IC 工作流程中,这种经过代工厂认证的方法使设计团队能够更有信心地从架构探索过渡到流片,从而降低晶圆堆叠、中介层实现和封装感知签核等环节在大批量生产环境中的风险。

这些3D-IC成功案例揭示了什么?

在这些 Cadence 3D-IC 案例研究中,涌现出几个共同的主题:

- 成功的3D-IC项目将封装视为首要的设计对象。

- 早期、综合的多物理场分析对于减少重自旋至关重要。

- 分层和分区方法对于可扩展性至关重要。

- 制造意识必须融入生产环节,而不是事后添加。

这些课程直接针对行业常见问题,包括 3D-IC 实现中的挑战、降低 3D-IC 设计功耗的策略以及 EDA 在实现可靠的异构集成中的作用。

扩大可重复3D-IC流片成功率

随着异构集成成为下一代系统的基础,设计成功不仅仅取决于创新的架构,还需要可重复、可量产且能够跨产品、节点和市场扩展的工作流程。

Cadence Integrity 3D-IC平台结合系统、功耗、信号和热分析功能,使团队能够自信地从概念阶段过渡到芯片阶段。这些Cadence 3D-IC的成功案例不仅展现了孤立的成果,更体现了一种可扩展的方法,能够在先进封装时代实现更快的带宽、更低的功耗和可预测的流片结果。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。