另辟蹊径,MIT攻克芯片堆叠的难关

麻省理工学院(MIT)的研究人员针对现代计算中最顽固的低效问题之一,即在逻辑单元和存储器之间移动数据所消耗的能量,提出了一种新的解决方案。该团队最近发现,通过在传统CMOS芯片的后端工艺(BEOL)中增加额外的有源器件层,他们可以将通常仅用于布线的区域转变为一个既能容纳逻辑晶体管又能容纳存储晶体管的堆叠结构。

研究人员在 IEEE IEDM(国际电子器件会议)上发表了两篇相关论文,重点分别是BEOL氧化铟晶体管和BEOL纳米级铁电存储器件。

当前面临的瓶颈

这一研究的出发点源于一种同样的 “架构税”,它持续占据着数据中心和边缘设备的电力预算。由于逻辑单元和存储器通常是独立的结构,每一个依赖于存储状态的计算步骤都迫使数据必须穿越互连层和封装边界。

这种数据移动既消耗能量又耗费时间,而且随着工作负载变得更加以数据为中心(包括深度学习和计算机视觉流水线),这种代价变得更加高昂。MIT将目标设定为:通过将更多功能元件紧凑地垂直堆叠在一起,来减少这种数据穿梭。

3D 堆叠并不是什么新技术,但在已完成的逻辑电路之上进行单片堆叠会受限于温度。标准的硅器件制造通常需要热预算,而这可能会损坏先前构建的晶体管和金属层。MIT团队的核心举措是避免 “从头开始” 构建新的硅器件,而是在芯片的后端(即传统上用于布线和金属键合的地方)添加有源层。

这种 “翻转” 至关重要,因为它将BEOL变成了额外的器件空间,而无需底层的CMOS承受另一轮高温的前端工艺流程。它还缩短了计算单元、嵌入式存储器和互连层之间的物理路径,而在传统布局中,这些路径是能量浪费的重灾区。

BEOL堆叠架构

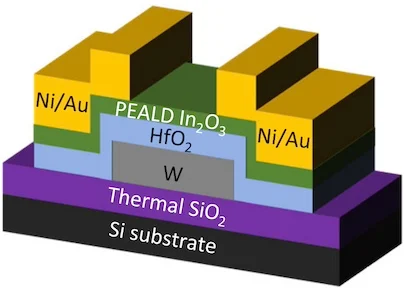

MIT 提出的架构是一个垂直集成的器件堆叠,制造于现有电路的后端,在已完成的 CMOS 之上形成了额外的有源晶体管层和存储元件。该堆叠中的核心器件是一种具有非晶氧化铟沟道层的 BEOL 晶体管。研究小组报告称,由于氧化铟的特性,他们能够在约 150°C 的温度下 “生长” 出一层极薄的薄膜,这一温度足够低,不会损害其下方的电路。

材料控制是制造过程中的主要挑战。在他们的工艺描述中,氧化铟薄膜只有约 2 纳米厚,其性能取决于缺陷管理。氧空位有助于沟道导电,但过多的空位会降低开关性能。该团队表示,他们优化了制造工艺,将缺陷降至最低,从而使最终器件能够 “快速且干净” 地开关,减少了与晶体管开关相关的额外能量损耗。

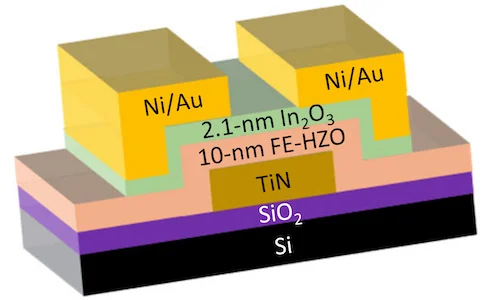

除了逻辑型BEOL器件外,研究人员还通过引入铁电铪锆氧化物(HZO)层,展示了具有集成存储功能的 BEOL 晶体管。这是一种实用的材料选择,因为基于氧化铪的铁电体已经成为与 CMOS 兼容的存储和计算概念的研究热点。据悉,这些器件尺寸约为 20 纳米,实现了 10 纳秒的开关速度(达到了团队的测量极限),同时工作电压低于同类器件。

其结果是一个可堆叠的平台,而不仅仅是单个器件的演示。一篇论文侧重于增强型 BEOL 氧化铟场效应晶体管及其建模,第二篇则针对 BEOL 纳米级铁电场效应晶体管中的铁电开关动力学。MIT还表示与滑铁卢大学在性能建模方面的合作,这一步骤通常在从孤立器件向电路级集成过渡中至关重要。

落地应用

MIT 的这项工作并不是要用氧化物电子学取代先进工艺节点的硅,而是要在当今芯片主要用于布线的地方增加新的功能层。然后,他们利用这种垂直集成来降低以数据为中心的计算的能源成本。最直接的受益者是那些存储器流量占主导的工作负载,包括需要重复传输激活值和权重的AI推理、深度学习和视觉任务。

同时这也涉及一个架构层面的角度,因为BEOL中具有存储能力的晶体管可以实现存储与计算之间更紧密的耦合,从而支持内存内计算(in-memory)和近内存计算(near-memory)方案。特别是铁电器件,经常被讨论用于高密度非易失性存储以及支持神经形态风格操作的模拟或多级行为。

MIT强调,将铁电存储晶体管缩小到纳米级尺寸,为团队提供了一个研究单个铁电单元物理特性的平台,这可能会影响未来存储和计算原语的设计。

短期内,这项工作可被视为一个工具和材料的里程碑,提供了一条低温、可控缺陷的路径,能够在不破坏现有结构的情况下,将有源晶体管和存储元件放置在已完成芯片的后端。下一步,MIT计划是将BEOL存储晶体管集成到单个电路中,并在改善对铁电层特性控制的同时推动器件性能的提升。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。