2026年,CPO将如何发展?

共封装光学(CPO)技术是下一代数据中心架构的核心使能技术,通过将光引擎与交换芯片紧密集成,有望实现前所未有的带宽密度和能效。然而,这项下一代光互连技术诞生已近十年,其大规模商业化落地目前处于何种阶段?

在深入探讨CPO的技术路线图及其未来部署前景之前,我们先对这一硅光架构进行简要介绍,看看它是如何为AI、HPC和高速网络应用提供助力。

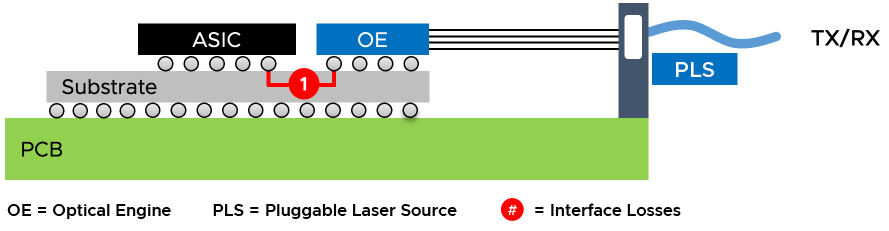

CPO 技术将光学组件直接集成于单一封装内,可最大限度缩短电信号传输路径,显著降低信号损耗、提升高速信号完整性,并有效控制延迟。换言之,CPO 通过采用高带宽光引擎提升数据吞吐量,与传统铜缆连接相比,光引擎不仅能实现更高的数据传输速率,还不易受电磁干扰(EMI)影响。

此外,这种硅光集成技术通过减少对高功耗电驱动器、中继器和重定时器的需求,进一步提升了能效。通过缩短铜质走线长度,CPO 可大幅优化链路预算,甚至无需数字信号处理器(DSP)或重定时器功能。这将显著降低每比特数据的整体功耗,而这也正是AI数据中心管理中的一项核心关键指标。

2025年CPO有哪些关键进展?

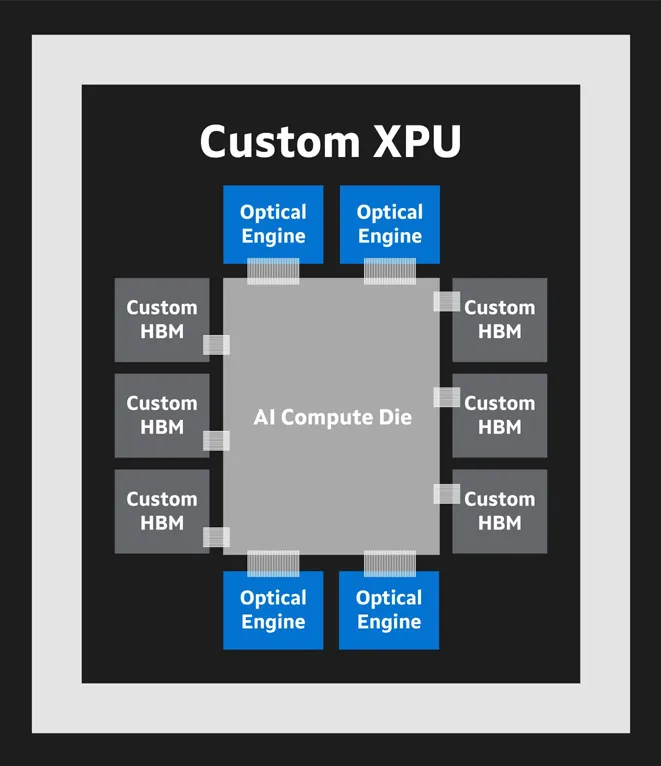

2025年1月,Marvell宣布其定制化 XPU 架构与CPO技术的集成取得重大突破。该公司展示了其定制化 AI 加速器架构如何通过SerDes、芯片间接口及先进封装技术,将 XPU 计算芯片、高带宽内存(HBM)及其他芯粒与 3D 硅光引擎集成于同一衬底之上。

这一设计使得电信号无需离开 XPU 封装即可传输至铜缆或PCB之外。此外,XPU 之间的连接不仅能实现更快的数据传输速率,传输距离也可达铜缆连接的 100 倍。Marvell的 3D 硅光引擎支持 200 Gbps 的电接口和光接口速率。

Marvell网络交换业务部高级副总裁兼总经理Nick Kucharewski表示:“AI 扩展型服务器需要更高的信号传输速率和更远的传输距离,以支持前所未有的 XPU 集群规模。将共封装光学技术集成到定制化 XPU 中,是通过更高的互连带宽和更远的传输距离实现性能扩展的必然下一步。”

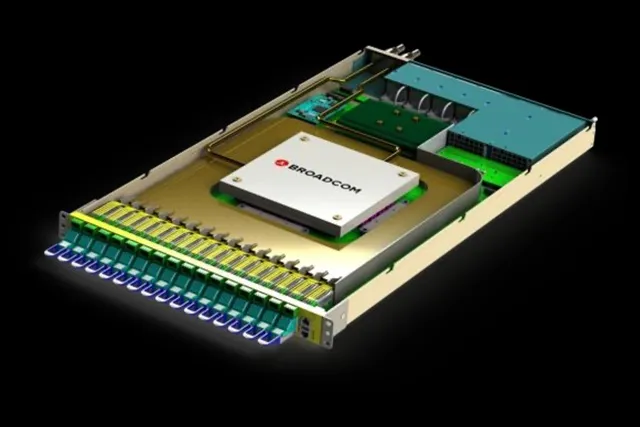

2025年5月,博通首次展示了其第三代每通道 200G 速率的CPO技术。博通的CPO研发之路始于 2021 年的 Tomahawk 4-Humboldt 芯片组,而其第二代产品 Tomahawk 5-Bailly 芯片组则成为业内首款实现量产的CPO解决方案。

博通光学系统事业部副总裁兼总经理Near Margalit表示:“博通已投入多年时间来完善CPO平台解决方案,第二代每通道 100G 产品的成熟度及生态系统的就绪程度便是最好的证明。” 该公司还声称,除了边缘交换机 ASIC 和光引擎技术外,其还拥有涵盖无源光学组件、互连产品及系统解决方案合作伙伴的完整生态系统。

2025年10月,博通宣布,Meta在高温实验室环境下对其CPO解决方案进行了总计 100 万链路小时的测试,期间未出现任何一次链路闪断。链路闪断指的是短暂的连接中断,是高性能数据中心网络中一项关键的可靠性指标。

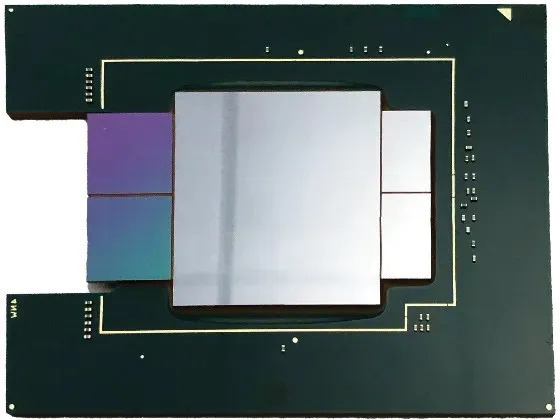

除了博通、Marvell等CPO行业巨头外,硅光领域也有不少值得关注的初创企业在致力于攻克I/O瓶颈。例如,光互连解决方案供应商Ayar Labs已将其 TeraPHY 光引擎整合至芯片设计企业GUC的 ASIC 设计服务中。

2025年11月,Ayar Labs宣布,其已将光引擎集成到GUC的先进封装和 ASIC 设计流程中,这是迈向未来CPO部署的关键一步。双方的联合设计工作有助于解决CPO集成过程中的核心挑战,包括架构设计、功耗与信号完整性、机械设计以及热管理等问题。

Ayar Labs首席技术官兼联合创始人Vladimir Stojanovic表示:“如果没有光学技术来攻克电 I/O 瓶颈,未来的 AI 和数据中心规模扩展将无从谈起。与GUC在先进封装和硅技术领域展开合作,是展示光引擎如何帮助超大规模数据中心运营商和 AI 扩展型企业加速共封装光学技术落地的重要一步。”

CPO技术未来如何发展?

尽管CPO技术的支持者迫切宣称CPO革命已近在眼前,但法国市场研究机构Yole Group等行业观察家认为,大规模部署要等到 2028 至 2030 年才会实现。在此期间,插装在 PCB 边缘交换机前面板的可插拔光模块仍将保持竞争力。

市场研究机构LightCounting也预测,在未来十年内,光模块仍将占据数据中心光链路的主导地位。不过,与此同时,光收发器技术也将持续稳步向 “光学组件靠近 ASIC” 的方向演进。

这是因为,随着交换机 ASIC 与光引擎之间的铜质走线长度不断增加,传统可插拔光模块在信号损耗、功耗和延迟方面正面临越来越大的限制。而CPO技术通过将光引擎放置在更靠近交换芯片的位置,成功克服了这些局限性。

光引擎向交换机 ASIC 的靠近,缩短了电信号传输所用铜质走线的长度,从而提升了电性能。然而,要将光引擎无缝集成到交换机 ASIC 或 XPU 中,需要多种封装技术的支持,包括 2.5D 中介层、硅通孔(TSV)、扇出型晶圆级封装,以及通过混合键合实现的 3D 集成技术。

随着这些先进封装技术的稳步发展,CPO 的部署进程也在持续推进。英国市场研究机构 IDTechEx 预测,到 2036 年,全球CPO市场规模将超过 200 亿美元,2026 至 2036 年期间的复合年增长率(CAGR)将高达 37%。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。