清华大学吴华强教授当选IEEE Fellow

近日,清华大学集成电路学院吴华强教授当选2026年度电气和电子工程师学会新晋会士(IEEE Fellow),以表彰他在忆阻器与存算一体技术领域的贡献(for contributions to resistive random-access memory and compute-in-memory technologies)。

IEEE Fellow 是美国电子电气工程师学会(Institute of Electrical and Electronics Engineers,简称IEEE)授予其会员的最高荣誉,获得IEEE Fellow荣誉是对个人在电气与电子工程、计算机、通信等领域所做出的杰出贡献和专业成就的高度认可,当选人需要对工程科学与技术的进步或应用作出重大贡献,为社会带来重大价值,每年仅有不到0.1%的会员能够获此殊荣。

吴华强教授现任清华大学党委常委、副校长。长期从事忆阻器与存算一体芯片技术研究,开展从底层器件到顶层架构协同创新,在国际上率先研制忆阻器多阵列存算一体系统和全系统集成的片上学习芯片,取得一系列特色鲜明的系统性创新成果,推动了后摩尔时代集成电路新原理器件、计算架构及前沿理论的深入发展。

吴华强教授先后主持了国家自然科学基金委重大项目、科技部科技创新2030重点项目等20余项科研项目,以通讯作者发表3篇Nature、Science正刊及近20篇子刊论文,成果多次被列入国际半导体技术路线图。授权发明专利100余项,多项专利实现成果转化,为国内忆阻器与存算一体芯片产业化作出重要贡献。他还担任IEEE EDS副主席,担任集成电路领域顶级国际会议IEDM/VLSI的技术委员会委员,在国际上具有广泛影响力。曾获国家杰出青年基金、首届科学探索奖、中国电子学会自然科学一等奖、北京高校优秀共产党员、北京市有突出贡献的科学、技术、管理人才等多项奖励。

基于忆阻器的压缩感知加速器:边缘计算新路径

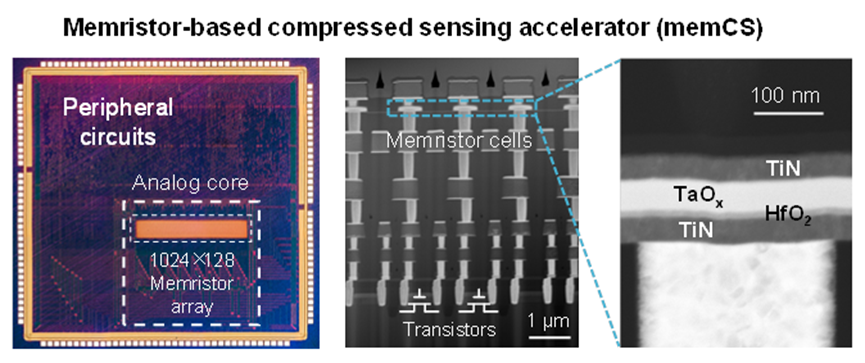

最近,清华大学唐建石、吴华强团队在《国家科学评论》(National Science Review, NSR)上发表论文,提出了一种基于忆阻器的压缩感知加速器(memCS)。基于所研制的128Kb忆阻器芯片,该加速器利用存算一体(CIM)架构高效并行加速矩阵-向量乘法,同时通过结合压缩感知的数学约束与忆阻器硬件的兼容性,构建了一套软硬件协同优化框架,解决了忆阻器非理想特性带来的精度损失问题。

边缘计算是一种将数据处理、应用程序和计算能力从中心的云服务器迁移到网络“边缘”——即更靠近数据源头(例如物联网设备、用户终端)的地方去执行的计算模式。随着人工智能和物联网的发展,边缘端感知设备需要处理飞速增长的感知数据。

压缩感知技术可以通过亚奈奎斯速率采样来降低感知设备的硬件开销,然而数据的重建过程仍受限于处理器和存储器之间的频繁数据搬运导致的高能耗与高延时。

128Kb忆阻器芯片的版图、芯片截面微观形貌图,以及忆阻器器件结构

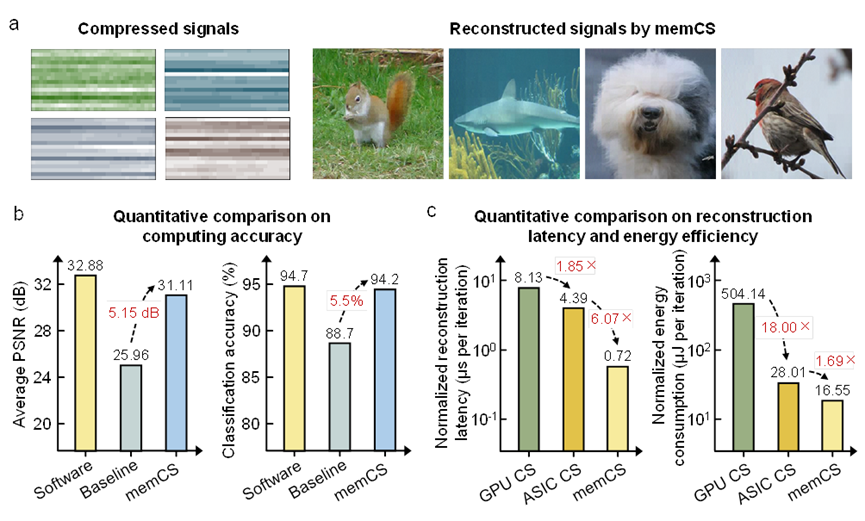

实验结果表明,在重建精度方面,经过协同优化的memCS实现了31.11 dB的平均峰值信噪比(PSNR)和94.2%的重建图像分类准确率,接近软件计算精度,且相较于未优化的基线分别提升了5.15 dB和5.5%;在系统性能方面,与GPU硬件相比,memCS实现了11.22倍的速度提升与30.46倍的能耗降低,展示出其在边缘计算应用中的优势。

memCS的边缘计算性能。(a)压缩信号与memCS重建信号。(b)压缩感知重建精度对比。(c)计算延时与能耗的评估结果对比。

该研究为用于边缘场景的高性能、高能效压缩感知系统的设计开辟了一条可行的路径。该项研究工作主要由清华大学集成电路学院完成,硕士生焦云锐与博士生赵涵为论文的共同第一作者,唐建石副教授与吴华强教授为通讯作者,合作者包括清华大学钱鹤教授、高滨教授以及天津大学孙彪教授等。该工作得到了科技创新2030重大项目、国家自然科学基金委、科学探索奖、北京集成电路高精尖创新中心以及清华大学微纳加工中心的资助与支持。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。