芯片验证不再卡壳,AI让芯片验证效率翻倍

在电子领域,集成电路(IC)芯片是推动进步的幕后推手。每一次飞跃——无论是更智能的手机、性能更强的汽车,还是医疗保健和科学领域的突破——都依赖于比以往任何时候都更复杂、速度更快、功能更强大的芯片。然而,制造这些芯片并非仅仅依靠卓越的工程技术或雄心壮志。芯片设计过程本身也达到了惊人的复杂程度,随之而来的是如何保持生产效率和产品质量不断提升的挑战。

随着我们不断突破物理极限,芯片制造商面临的挑战远不止技术难题。劳动力短缺、时间紧迫以及对可靠芯片的制造要求都比以往任何时候都更加严格。为了确保芯片布局符合详细的约束条件,例如保持晶体管和导线的最小特征尺寸、保持金属层、多晶硅层和有源区等不同层之间的适当间距,以及确保过孔正确重叠以形成牢固的电气连接,需要投入大量的精力。这些设计规则随着每一代新技术的出现而不断增加。每一次创新都伴随着以更少的资源实现更多目标的压力。因此,问题就变成了:我们如何帮助设计人员满足这些要求?技术又如何帮助我们在不牺牲质量的前提下应对这些复杂性?

范式转变:人工智能在电子设计自动化领域的崛起

一场变革浪潮正席卷整个电子设计自动化(EDA)领域。EDA是芯片制造商用来设计、分析和验证当今芯片内部复杂集成电路的软件和工具的专业领域。人工智能已经渗透到芯片设计流程的诸多环节——辅助布局布线、预测良率、优化模拟电路、自动化仿真,甚至指导早期架构规划。人工智能并非仅仅加速传统流程,而是为全新的思维和工作方式开辟了道路。

机器学习模型可以帮助预测缺陷热点或优先考虑风险区域,而无需等到芯片送去制造。

人工智能无需进行蛮力计算或编写无数行自定义代码,而是利用先进的算法来发现模式、整理海量数据集并突出显示问题,而这些问题如果通过人工方式发现可能需要数周时间。例如,生成式人工智能可以帮助设计人员用自然语言提出问题并获得答案,从而简化日常任务。机器学习模型可以在芯片送去制造之前很久就帮助预测缺陷热点或确定风险区域的优先级。

人类专业知识与机器智能之间日益紧密的合作,正为所谓的“左移”或并行构建革命铺平道路——在设计过程的早期阶段就发现并解决问题,避免其演变成代价高昂的挫折。对于芯片制造商而言,这意味着更高的产品质量和更快的上市速度。对于设计人员而言,这意味着他们有机会专注于创新,而不是疲于应对各种缺陷。

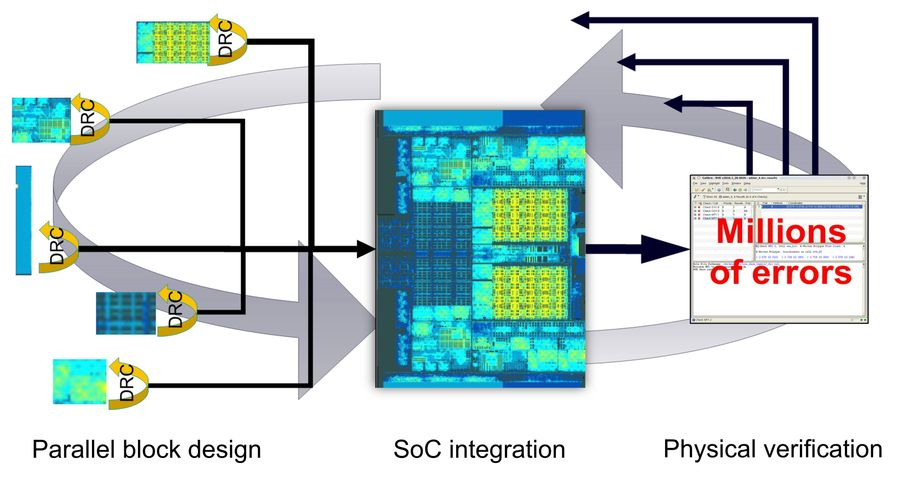

图 1. 左移和并行构建集成电路芯片可以同时执行多个以往需要顺序完成的任务。来源:西门子

物理验证瓶颈:为什么设计规则检查比以往任何时候都更加困难

随着芯片变得越来越复杂,设计过程中被称为物理验证的部分成为了关键瓶颈。物理验证检查芯片布局是否符合制造商的严格规定,并与原始功能原理图完全一致。其主要目标是确保设计能够可靠地制造成可正常工作的芯片,并且不存在可能导致后续故障的物理缺陷。

设计规则检查 (DRC) 是物理验证的基石。DRC 软件会扫描芯片布局的每个角落,查找违规之处——这些违规可能导致缺陷、降低良率,甚至使设计无法制造。但如今的芯片不仅体积更大,而且结构更加复杂,由多层逻辑、存储器和模拟元件交织而成,有时甚至以三维方式堆叠。规则也变得不再简单。它们可能取决于几何形状、上下文、制造工艺,甚至取决于布局中远距离特征之间的相互作用。

传统上,设计规则检查(DRC)是在流程后期进行的,此时所有组件都已组装成最终的芯片布局。在这个阶段,通常会发现数百万个违规项——而修复这些后期问题需要耗费大量精力,导致代价高昂的延误。

为了减轻这种负担,人们越来越重视将设计规则检查 (DRC) 提前到流程早期阶段——这种策略被称为“左移”。工程师们不再等到整个设计完成才进行 DRC 检查,而是尝试在模块和单元级别更早地识别和解决 DRC 错误。这种并行设计和验证方法使得大部分错误能够在修复速度更快、干扰更小的时候被发现。

然而,在芯片设计流程早期,当各个模块尚未通过DRC检查时就对整个芯片运行DRC,会产生规模惊人的数据集——通常会有数千万到数十亿个“错误”、警告或标记,因为与已经完成完整设计流程的芯片相比,未完成的芯片设计“不干净”。处理这些“不干净”的结果本身就是一项挑战。设计人员必须确定优先处理哪些问题,识别指向系统性问题的模式,并决定哪些才是真正重要的。在许多情况下,这项工作缓慢且需要“手动”完成,取决于工程师筛选数据、过滤重要信息以及在团队之间共享发现的能力。

为了应对信息过载,设计团队想方设法限制信息量。他们可能会限制每条规则的错误数量,或者使用一些非正式的捷径——例如通过电子邮件将数据库或屏幕截图发送给团队成员,在聊天信息中共享过滤器,以及依赖专家来查找问题。然而,这种方法并不可持续。它可能会遗漏一些影响芯片整体的重大问题,而这些问题可能会波及最终产品。此外,它还会减慢响应速度,并使协作变得极其耗费人力。

随着劳动力短缺的持续存在和现代芯片复杂性的不断提升,对更智能、更自动化的DRC分析的需求变得迫切。那么,更好的解决方案会是什么样的?人工智能又如何帮助弥合这一差距?

人工智能驱动的DRC分析的兴起

人工智能的最新突破彻底改变了错误率分析的格局,这在几年前是难以想象的。人工智能系统不再需要逐行或逐项扫描,而是可以处理数十亿个错误,将它们聚类成有意义的组,并帮助设计人员更快地找到根本原因。这些工具运用计算机视觉、高级机器学习和大数据分析等技术,将曾经看似无穷无尽的信息转化为行动路线图。

人工智能能够整理混乱的数据集,发现隐藏在多个规则或区域中的系统性问题,从而帮助识别基本过滤方法可能遗漏的风险。通过对相关错误进行分组并突出显示热点区域,设计人员可以把握全局,并将时间集中在关键之处。基于人工智能的聚类算法能够可靠地将数周的人工调查转化为几分钟的引导式分析。

人工智能系统可以处理数十亿个错误,将它们聚类成有意义的组,并帮助设计人员更快地找到根本原因。

另一项优势在于协作。现代工具将结果视为共享的动态数据集,而非静态表格,使团队能够指定负责人、注释发现,并在模块工程师和分区工程师之间传递精确的分析视图,甚至跨越组织边界。动态书签和共享的用户界面状态减少了混乱和返工。团队不再需要“来回沟通”,而是携手并进。

这些创新成果大多展现了将人工智能融入验证流程核心所能带来的无限可能。它们不仅能帮助设计人员分析结果,还能帮助所有人理解数据、总结发现,并在整个流程中做出更优的设计决策,直至最终流片。

西门子 Calibre Vision AI 在 DRC 分析和协作方面取得的真正突破

西门子提供的Calibre Vision AI 平台是人工智能驱动的 DRC 分析领域最引人注目的案例之一,它为全芯片验证树立了新的标准。凭借多年在物理验证方面的经验,西门子意识到,突破瓶颈不仅需要更智能的算法,还需要重新思考团队协作方式以及数据在整个流程中的流动方式。

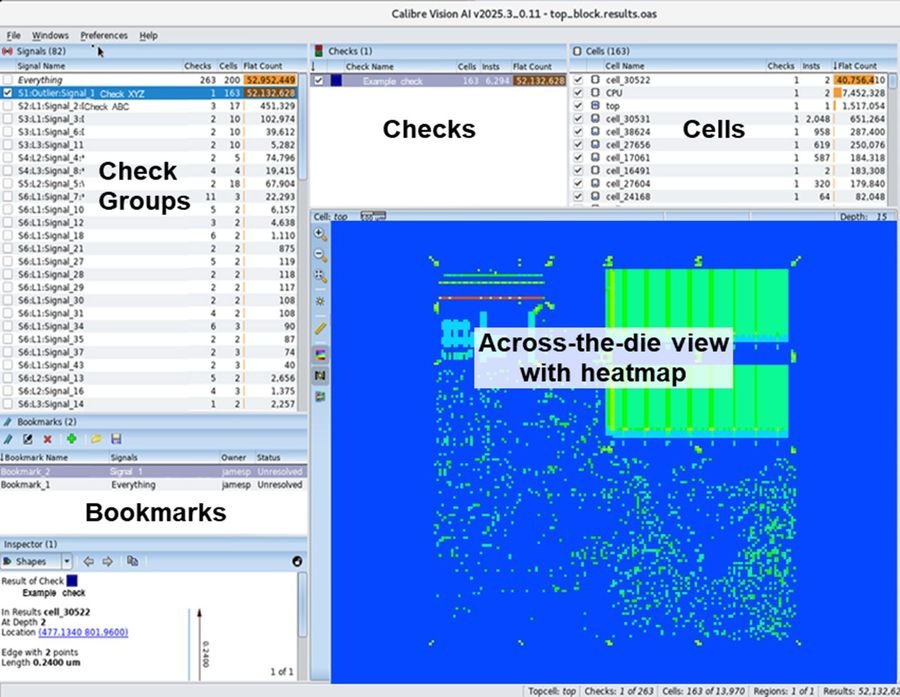

Vision AI 的设计兼顾速度和可扩展性。它采用紧凑的错误数据库和多线程引擎,可在数分钟内加载数百万甚至数十亿个错误,并将其可视化,使工程师能够看到整个芯片上的错误集群和热点区域。该工具不会显示大量的错误代码或孤立的规则违规,而是呈现布局的热图,突出显示问题最集中的区域。通过启用或禁用图层(布局、标记、热图)并调整图层不透明度,用户可以清晰、自定义地了解当前情况,并确定下一步的检查方向。

Vision AI 利用先进的机器学习算法,分析每一个错误,找出具有共同故障原因的组。

但真正的魔力在于人工智能引导的聚类。Vision AI 利用先进的机器学习算法,分析每一个错误,找出具有共同故障原因的组。这意味着设计人员可以一次性解决数百个检查项的根本原因,而无需逐个进行繁琐的排查。例如,如果使用传统工具,团队可能需要耗费大量精力来处理 3400 个检查项和 6 亿个错误;而 Vision AI 的聚类功能可以将工作量减少到仅需调查 381 个组——化繁为简,并将调试时间至少缩短一倍。

图 2. Calibre Vision AI 软件可自动执行并简化芯片级 DRC 验证流程。来源:西门子

Vision AI 还具有高度协作性。动态书签能够精确记录分析状态,从图层过滤器到缩放的布局区域,以及注释和负责人分配等信息。共享书签会将实时分析结果(而非静态快照)发送给同事,确保每个人都能从同一视图进行工作。团队可以导出结果数据库,将可执行的操作分组分配给模块负责人,并将分析结果无缝导入到其他西门子 EDA 工具中进行进一步调试。

赋能每一位设计师:缩小专业知识差距

芯片验证中一个常见的痛点是需要深厚的专业知识——了解哪些错误至关重要,哪些模式意味着问题,以及如何解读复杂的结果。Calibre Vision AI 有助于消除这种不公平竞争。其基于人工智能的算法能够始终如一地创建与资深专家相同的集群和调试路径,而且只需几分钟即可完成。新用户也能快速发现系统性问题,并像经验丰富的工程师一样高效工作,从而帮助芯片公司应对人员短缺和人员流动问题。

除了集群和书签功能外,Vision AI 还允许设计人员利用自身数据构建自定义信号。该平台可确保客户模型和数据的安全,供其专属使用,从而保障敏感信息在公司内部的保密性。此外,通过与西门子 EDA AI 生态系统集成,Calibre Vision AI支持生成式 AI聊天机器人和推理助手。设计人员可以直接提问——例如关于语法、信号或流程的问题——并获得快速准确的答案,从而简化培训和推广流程。

实际成果:加快分析速度并分享洞见

来自领先集成电路公司的客户反馈表明,人工智能在全芯片设计规则检查 (DRC) 分析和调试方面具有切实价值。一家公司报告称,Vision AI 至少减少了他们一半的调试工作量——这一节省足以决定芯片能否顺利流片。另一家公司指出,该平台的信号算法能够自动创建经验丰富的用户需要手动识别的检查组,从而节省了时间和精力。

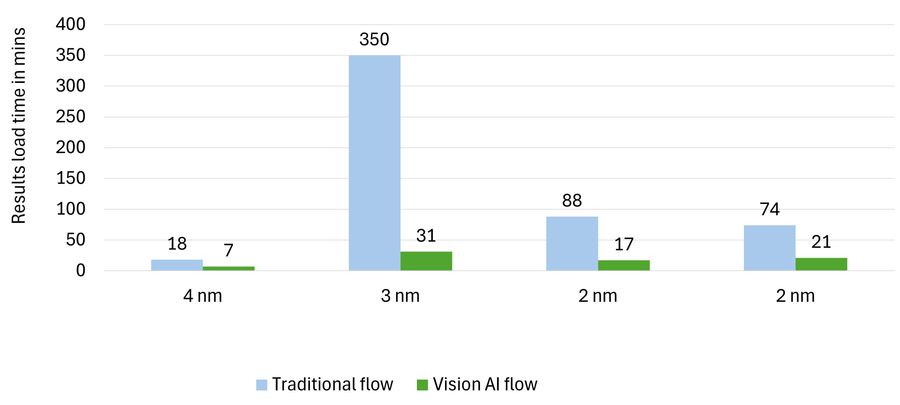

量化方面的提升非常显著。例如,Calibre Vision AI 加载和可视化错误文件的速度远超传统调试流程。图 3 展示了四个不同测试用例的差异:传统流程需要 350 分钟才能处理完的结果文件,而 Calibre Vision AI 仅需 31 分钟。在另一个测试用例(图中未显示)中,仅用了五分钟就分析并聚类了来自 380 多个规则检查的 32 亿个错误,将其归纳为 17 个有意义的组。设计人员现在无需再被海量的错误数据所困扰,而是可以将时间用于解决实际问题。

图 3. 传统 DRC 调试流程与 Calibre Vision AI 流程的结果加载时间对比图。来源:西门子

展望未来:人工智能在芯片设计领域的未来

如今的芯片对EDA软件的要求已远不止于渐进式改进。随着对速度、质量和协作的需求不断增长,物理验证的未来将由更智能、更具适应性的技术来塑造。借助AI驱动的DRC分析,我们看到了清晰的发展路径:更快、更高效地发现系统性问题,实现智能调试,加强协作,并让每位设计人员都有机会发挥专家级的作用。

Calibre Vision AI等平台将工程师的创造力与人工智能的速度和洞察力相结合,正在推动全芯片分析领域生产力的大幅提升。借助这些工具,团队不仅能够应对复杂性,还能将其转化为竞争优势。

在西门子,芯片验证的未来已初具雏形——智能与直觉相辅相成,新理念以前所未有的速度转化为芯片。随着行业不断突破界限,开启下一代器件的时代,人工智能将助力芯片设计迈上新的高峰。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。