别只盯光刻机,光罩更关键

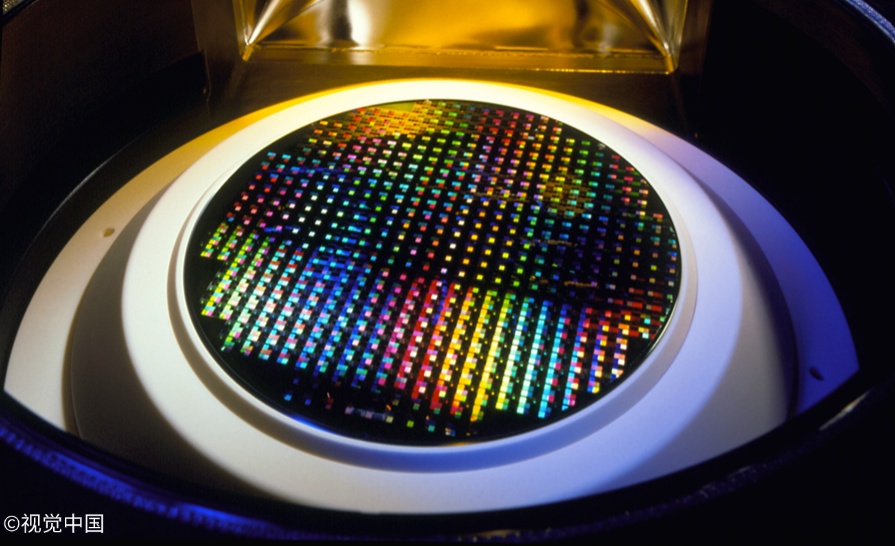

当一颗指甲盖大小的芯片里塞进百亿个晶体管时,很少有人会追问:这些比细菌还小的电路图案,最初是怎么"画"出来的?答案藏在一块看似普通的石英玻璃背后——光罩,这个被业内称为"半导体母版"的关键器件,正以纳米级的精度定义着芯片的极限性能。

光罩三百年进化史

如果回溯光罩的前世今生,会发现它的进化史就是一部微观制造的精度竞赛史。18世纪末,法国人约瑟夫·尼塞福尔·涅普斯用沥青涂层的锡版制作了世界上第一块"光罩",通过日光曝光将窗外景色印在金属板上——这种原始的成像逻辑,与今天半导体光罩惊人地相似。只是当年的"像素"是毫米级的色块,而今已缩小到0.5纳米,相当于把地球按比例缩小到乒乓球大小的精度控制。

1990 年代末,随着半导体进入深亚微米时代,光罩技术迎来最剧烈的变革期。KrF(248nm)光刻技术要求光罩线宽达到 180nm,这意味着需要检测直径仅 50nm 的缺陷 —— 相当于在标准足球场大小的区域内找出一颗尘埃。为应对挑战,光罩制造引入了原子层沉积(ALD)技术,实现铬层厚度控制在 ±0.1nm 范围内;同时开发了激光修复系统,通过聚焦离子束(FIB)精确移除缺陷,修复精度达 10nm 级。

现代光罩的核心结构看似简单:在高纯度石英玻璃上,用铬层蚀刻出电路图案。但在实际制造中,这块"玻璃片"需要经过30多道工序的雕琢。日本信越化学生产的光罩基板,每平方厘米的平整度误差不能超过0.3纳米。

2024年三星推出的3nm GAA工艺中,光罩技术实现了一次关键突破:采用"自对准多重曝光"(SAQP)技术的光罩组,通过四次叠加曝光,在物理分辨率有限的情况下,"画"出了间距仅7nm的鳍片场效应晶体管(FinFET)。这就像用4张不同角度的底片,在同一张相纸上叠加出立体影像,只不过这里的"相纸"是单晶硅,"影像"是能导电的纳米结构。

产业链的“咽喉要道”

光刻工艺堪称半导体器件制造工艺的核心步骤之一,光刻成本约占整个硅片制造工艺的 1/3,耗费时间约占整个硅片工艺的 40%-60% ,而光罩在其中扮演着无可替代的 “投影模版” 角色。其工作流程极为精密复杂,首先由特定光源发出光线,如 248nm 的 KrF(氟化氪)准分子激光常用于 90nm 至 0.25μm 制程节点,193nm 的 ArF(氟化氩)准分子激光则支撑着从 65nm 到目前先进的 3nm 制程 。光线透过光罩的透明区域,这里的透明区域与遮光区域由铬层等材料精准界定,进而将光罩上精心设计的电路图案投影到涂有光刻胶的晶圆表面,这一关键步骤即为曝光。

在曝光过程中,光刻胶会因吸收光子能量而发生光化学反应。对于正性光刻胶,曝光区域的光刻胶在显影液中溶解度大增;负性光刻胶则相反,未曝光区域在显影液中溶解。经显影处理后,晶圆表面便形成与光罩一致的图案。此后,利用刻蚀工艺,如等离子体刻蚀,通过高能离子束对晶圆进行轰击,将显影后的光刻胶图案转移到晶圆上的特定材料层,去除不需要的材料部分,留下所需的电路结构。

值得一提的是,光罩上的图案一般是电路设计图的 4 倍大小,这种放大设计便于在光罩制作阶段对图案进行更精准的加工与修正。通过光刻机先进的投影系统,如采用多组高精度透镜组成的光学系统,将光罩图案缩小到 1/4 后投影到晶圆上 。这种缩小操作基于光学成像原理,不仅提高了分辨率,理论上分辨率与曝光波长成正比,与投影系统的数值孔径成反比,缩小图案相当于变相缩短了曝光波长,还降低了制造误差。因为在缩小过程中,图案边缘的微小偏差被大幅缩小,使得最终在晶圆上形成的电路图案更为精准。

可以形象地说,光罩就如同投影仪的“幻灯片”,借助光的投射,把图案清晰地映射到 “屏幕”—— 晶圆之上。但与普通幻灯片不同,光罩制作需历经 30 多道工序,从高纯度石英玻璃基板的选择,像日本信越化学生产的光罩基板,每平方厘米的平整度误差不能超过 0.3 纳米 ,到铬层等遮光层的精准蚀刻,再到图案的电子束或激光直写绘制,每一步都对精度和环境洁净度有着严苛要求,其复杂程度和技术门槛极高,是半导体制造中名副其实的 “咽喉要道”,决定着芯片制造的精度与性能 。

谁在掌控光罩话语权?

掌握高端光罩,尤其是EUV光罩的核心技术与制造能力,已成为决定先进芯片制造话语权的关键一环。当前,这一领域的竞争格局高度集中,少数几家掌握顶尖技术的企业牢牢把控着产业链的关键节点。

审视全球光罩产业链,话语权的分布呈现出明显的“金字塔”结构,塔尖由日本、美国及部分欧洲企业构成,它们在高端光罩制造、核心材料供应及尖端检测设备领域占据绝对主导地位。

美国的 Photronics 作为全球领先的独立第三方光罩制造商,在半导体、平板显示等多个领域的光罩制造方面具有深厚的技术积累。该公司成立于 1969 年,经过多年的发展,通过持续的研发投入和技术创新,掌握了一系列先进的光罩制造技术。在光学邻近校正(OPC)技术方面,Photronics 能够通过精确的算法和先进的软件工具,对光罩上的图案进行优化,以补偿光刻过程中的光学畸变,从而提高芯片制造的精度和良率。

日本在光罩产业的优势更为显著,不仅在高端光罩制造企业数量上占据优势,而且在光罩制造的全产业链环节都具备强大的技术实力。除了 Toppan 和 DNP 在高端光罩制造领域的领先地位外,日本企业在光罩基板、光刻胶等关键材料以及光罩制造设备等方面也处于全球领先水平,豪雅(Hoya)和信越化学(Shinetsu)是全球最大的两家供应商,市场份额合计超过 90% 。豪雅生产的光罩基板具有极高的平整度和光学性能,其采用的先进熔炼和加工工艺能够确保基板在不同环境条件下都能保持稳定的性能,为高端光罩的制造提供了坚实的基础。信越化学则在高纯度石英材料的生产方面具有独特的技术优势,其生产的石英基板在杂质含量控制、热稳定性等方面表现出色,广泛应用于 EUV 光罩等高端产品。

在光刻胶方面, JSR、东京应化(TOK)等企业占据了全球半导体光刻胶市场的主要份额。光刻胶作为光罩制造和芯片光刻过程中的关键材料,其性能直接影响到光罩图案的转移精度和芯片制造的质量。日本企业通过长期的研发投入和技术创新,开发出了一系列高性能的光刻胶产品,能够满足不同制程节点的需求。例如,JSR 的 ArF 光刻胶在分辨率、灵敏度和抗刻蚀性能等方面表现优异,被广泛应用于 14nm 及以下先进制程的芯片制造。

长期以来,中国大陆的光罩产业在全球产业链中处于相对弱势地位。在 2020 年以前,国内光罩厂数量虽不少,但整体技术水平较低。以当时知名的 “三兄弟”—— 清溢光电、路维光电和龙图光罩为例,其工艺能力大多集中在 0.25 - 0.5 微米之间;中微掩模电子的能力稍优,可达到 0.13 微米。

近年来,随着国家对半导体产业的高度重视以及产业政策的大力扶持,国产光罩迎来了快速发展的黄金时期。龙图光罩自 2010 年入局半导体掩模版业务,经过多年的技术攻关,将工艺节点从 1μm 提升至 130nm。

2023 年底,龙图光罩成功过会,拟募资投向高端半导体芯片掩模版制造基地等项目,加速 130nm 以下制程光罩的国产化进程。该公司在高精度半导体掩模版领域持续进行设备引进与技术攻关,针对半导体掩模版的工艺特点,掌握了图形补偿技术、精准对位标记技术、光刻制程管控技术、曝光精细化控制技术、缺陷修补与异物去除技术等多项自主研发的核心技术,涵盖 CAM、光刻、检测三大环节。同时,积极开展技术布局与储备,储备了电子束光刻技术及 PSM 相移掩模版技术,形成了一定的技术成果。目前,龙图光罩已实现 130nm 工艺节点半导体掩模版的量产,具备 ±20nm 的 CD 精度和套刻精度,其技术实力和工艺能力在国内第三方半导体掩模版厂商中居于领先地位。其产品已经通过了中芯集成、士兰微、积塔半导体、新唐科技、比亚迪半导体、立昂微、燕东微、粤芯半导体、长飞先进、扬杰科技等多个国内知名晶圆制造厂商的认证。

清溢光电也在不断突破,作为国内规模最大的国产光掩模供应商之一,该公司在半导体光罩领域持续投入研发,产品逐步从中低端向中高端迈进。通过与国内科研机构合作,引进先进人才,清溢光电在光罩制造的关键技术环节取得了重要进展,如在光罩的缺陷检测与修复技术方面,开发出了具有自主知识产权的检测算法和修复工艺,有效提高了光罩产品的质量和良品率。其产品不仅在国内市场份额稳步提升,还开始涉足国际市场,与国际大厂展开竞争,产品出口到韩国、日本等半导体产业发达的国家和地区。

路维光电同样成绩不错,实现了 250nm 制程节点半导体掩膜版量产,掌握 180nm/150nm 节点核心技术,产品广泛应用于多个领域,为国内半导体产业提供了有力支撑。

结语

光罩这小小的玻璃片,说到底是场关于"把事做细"的较量。从几百年前用沥青锡版印风景,到现在在纳米尺度画电路,人们总在琢磨怎么把图案做得更准、更小。

那些厉害的国际厂商,无非是把每个细节抠到了极致——基板要平到几乎没有误差,材料要纯到挑不出杂质。这些事,现在国内的厂子也在一步步做,可能还没到最顶尖,但每一步都走得扎实。

龙图光罩实现130nm 光罩的稳定量产,清溢光电掌握自主的缺陷修复技术,路维光电在成熟领域打磨出可靠工艺,这些都是看得见的进步。无需宏大的叙事,只是把手上的技术做精做透,让下游厂商用得安心顺手。

将来也许没人会特意打听光罩是谁做的,就像现在没人纠结铅笔是谁造的。但眼下这些一点点磨出来的精度、攒出来的经验,总会变成底气——证明在这行里,咱们能把该做的事做好,能跟上趟,甚至慢慢走出自己的路。

这就够了。

此内容为平台原创,著作权归平台所有。未经允许不得转载,如需转载请联系平台。