英特尔18A技术细节:性能密度提升30%,同功耗下频率提升25%

近日,英特尔展示了即将推出的Intel 18A工艺的详细情况,该工艺节点将取代Intel 3节点,提供更好的时钟和电压调节,计划于2025年下半年进入大规模生产,预计Panther Lake客户端处理器以及Clearwater Forest至强处理器将会采用该工艺节点。

Intel 18A工艺节点结合了RibbonFET(GAA环绕栅极晶体管)和PowerVia(背面电源传输),从而形成全新的金属堆叠架构。

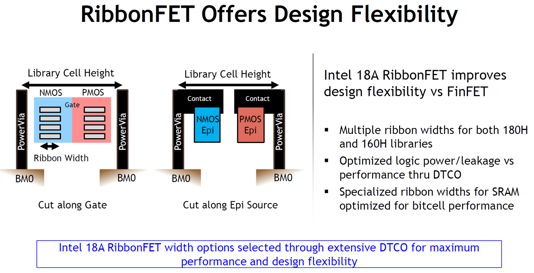

其中,RibbonFET采用的栅极静电特性,单位面积有效宽度更大、寄生电容更低,设计灵活性进一步提升。为180H/160H库引入多种Ribbon宽度,通过DTCO(设计工艺协同优化)平衡逻辑功耗/漏电与性能,为SRAM定制Bitcell优化的Ribbon宽度,全面增强 18A 节点芯片性能与设计潜力。

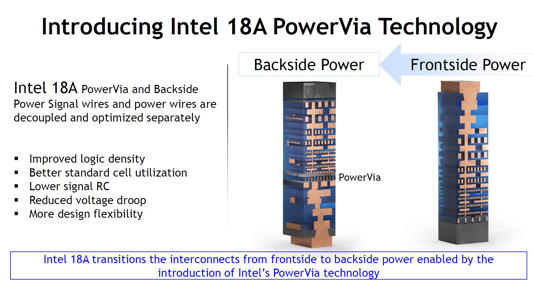

PowerVia技术以背侧供电走线替代前侧走线,实现供电网络解耦与独立优化,从而实现多重增益:逻辑密度提升;标准单元利用率改善;信号 RC 值降低;电压降(droop)收缩;设计灵活性进一步实现拓展。其将密度和单元利用率提高5%至10%,并降低电阻导致的供电下降,从而使ISO功率性能提高4%。

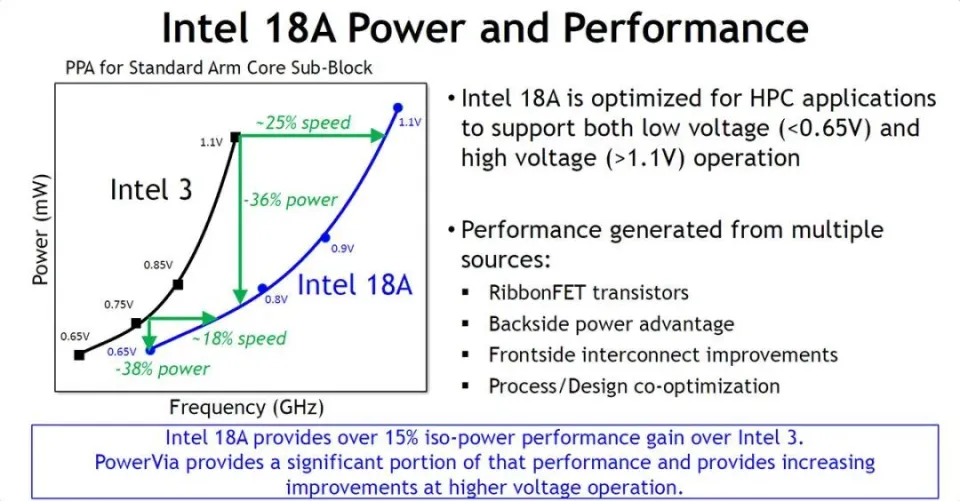

与Intel 3工艺节点相比,Intel 18A的每瓦性能提高了15%,芯片密度提升了30%。具体来看,Intel 18A在低电压(<0.65V)和高电压(>1.1V)下均表现出色。在相同功耗下,其性能比Intel 3提升18%-25%;在相同频率下,功耗则降低36%-38%。

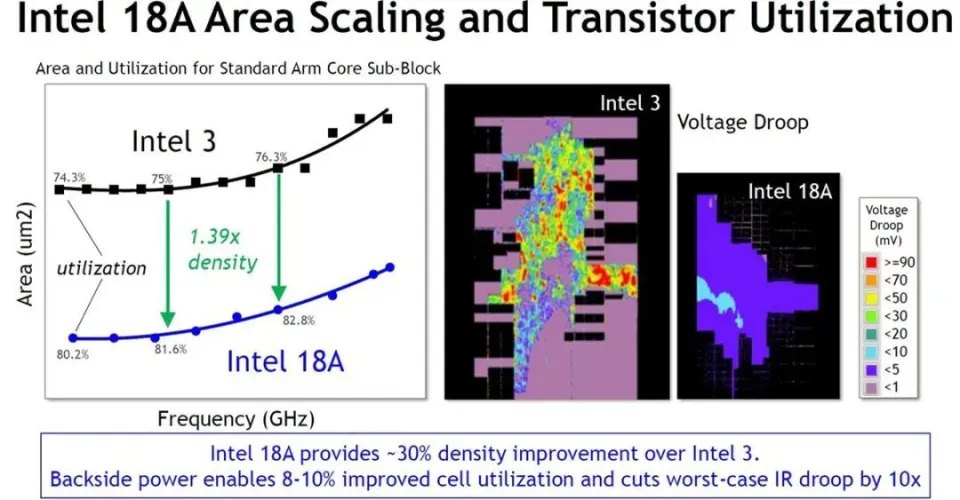

在芯片面积缩放和利用率方面,Intel 18A相比Intel 3带来了最高39%的密度提升(平均约30%),单元利用率也提升了6.5个百分点。此外,PowerVia技术的应用使单元能源利用率提高了8%-10%,并将最坏情况下的固有电阻下降降低了10倍。

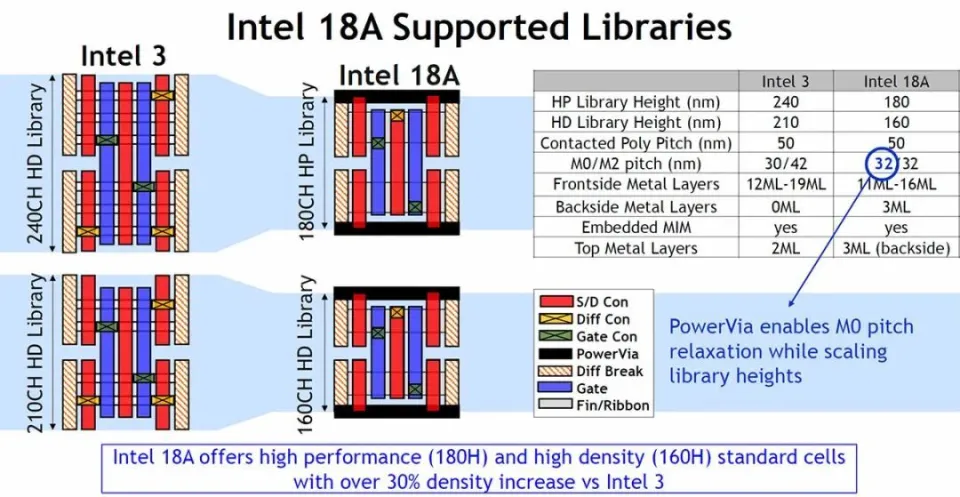

Intel 18A的单元高度在使用高性能设计时从240nm降低至180nm,采用高密度设计则从210nm降低至160nm,而M0/M2间距从30/42nm变成了32/32nm,正面金属层数从Intel 3的12~19层减少到11~16层,并增加了三个背面金属层以支持PowerVia。M1至M10层的间距已从60nm缩小至32nm,之后在上层再次放宽。M0至M层采用低数值孔径EUV曝光技术,将所需光罩数量减少了44%,并简化了制造流程。

在互连性能方面,Intel 18A显著降低了通孔电阻。相比Intel 3,其M0/M3/M6层的通孔电阻分别降低了24%、30%和49%,M40-M42层降低了12%,M80-M84层降低了13%。

此外,在SRAM缩放方面,Intel 18A的HCC SRAM单元面积为 0.0230 μm² 、HDC SRAM单元面积为 0.0210 μm²,相比于Intel 3,分别缩小了23.3%和12.5%。不过,与台积电N2制程相比,Intel 18A的SRAM密度仍存在一定差距。此前曝光的信息显示,台积电N2制程的HDC SRAM单元面积为 0.0175 μm²。在SRAM Vmin性能方面,Intel 18A提供了HCC bitcell单元和HDC bitcell单元,均符合行业标准SRAM Vmin规格。其中,带写辅助HCC bitcell单元相比不带写辅助的电压可降低70mV。

英特尔表示,Intel 18A目前已进入风险试产阶段,预计将在年底实现大规模量产,首发应用于Panther Lake客户端处理器和Clearwater Forest服务器处理器。尽管英特尔与NVIDIA、博通等合作伙伴已展开基于Intel 18A的芯片测试验证,但其财务总监戴维·津斯纳表示,目前该技术对外部客户的代工规模尚不显著。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。