英特尔18A工艺节点技术细节:较Intel 3实现30%以上密度提升

英特尔在 2025 年超大规模集成电路技术与电路研讨会(Symposium on VLSI Technology and Circuits)上披露下一代 Intel 18A 工艺节点技术细节。

该节点将取代现有 Intel 3 节点,优化频率与电压调节能力,后续将应用于消费级处理器“Panther Lake”以及服务器处理器 Clearwater Forest(纯 E 核 Xeon)等产品。

据英特尔工程师介绍,采用 RibbonFET(全环绕栅极 GAA)与 PowerVia(背侧供电)技术的 Intel 18A 制程相较 Intel 3 实现了 30% 以上密度提升与“全节点性能进步”,同时提供高性能(HP)、高密度(HD)库,兼具完整设计能力与易用性。

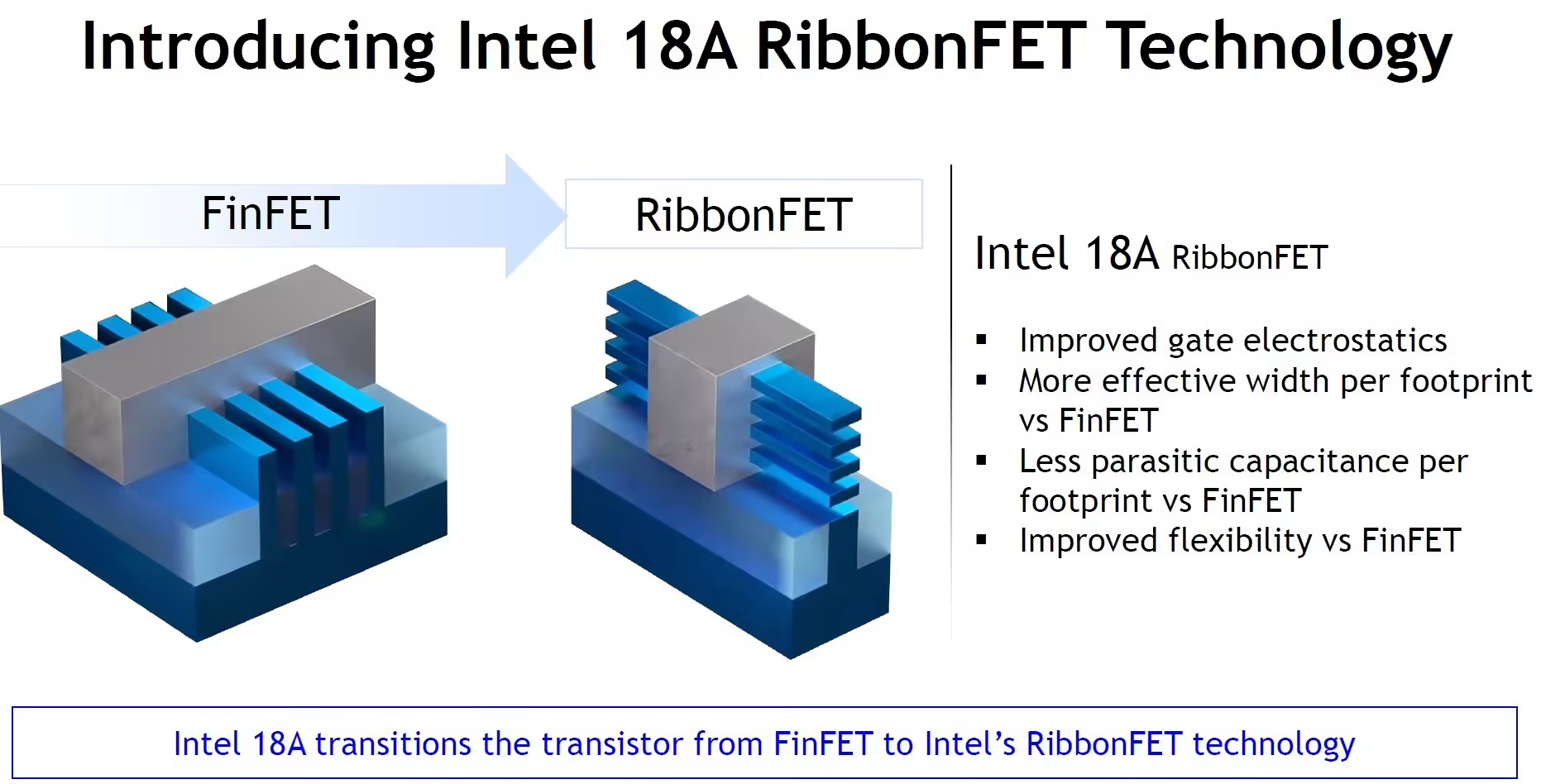

得益于 RibbonFET 技术,Intel 18A 相较于使用 FinFET 的 Intel 3 实现大幅跨越。RibbonFET 主要优势在于:

优化栅极静电特性,单位面积有效宽度更大、寄生电容更低,设计灵活性进一步提升;

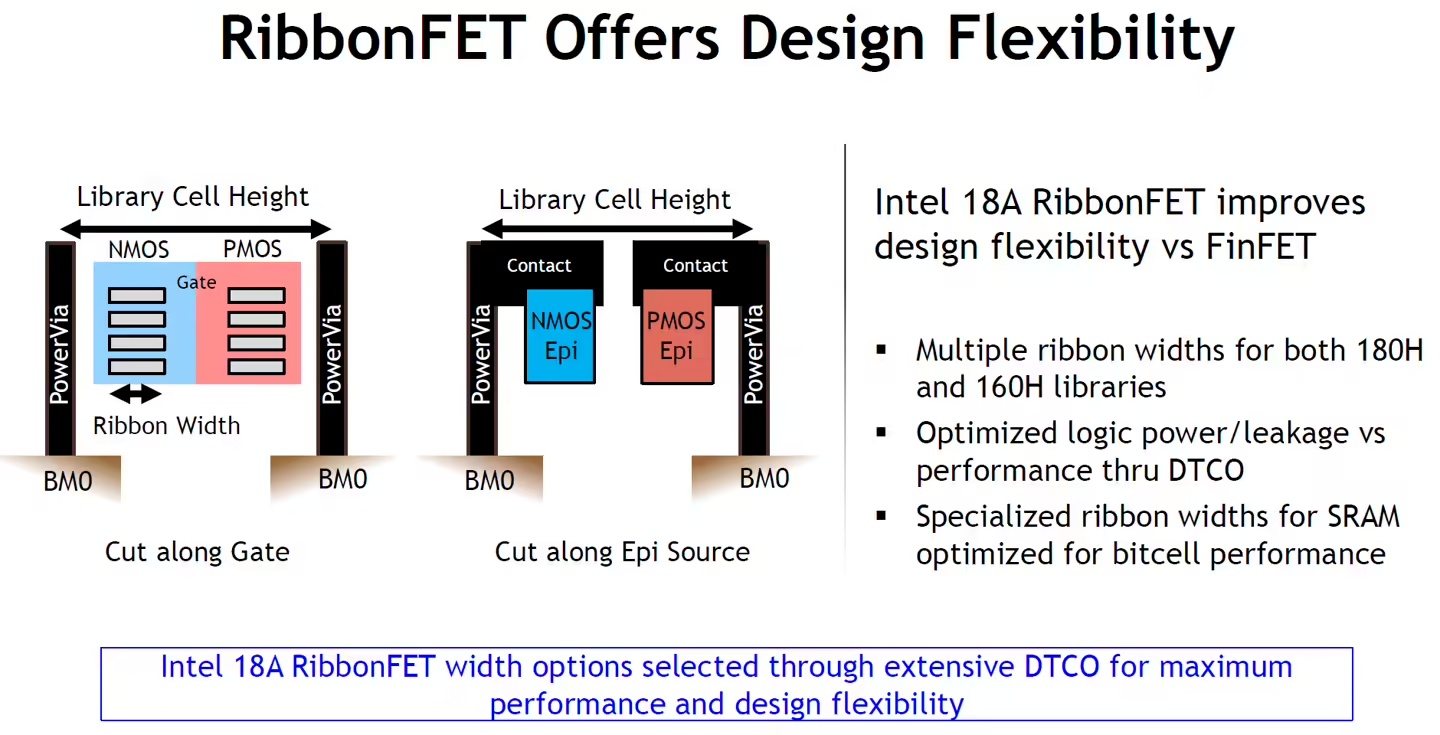

为 180H / 160H 库引入多种 Ribbon 宽度,通过 DTCO(设计工艺协同优化)平衡逻辑功耗 / 漏电与性能,为 SRAM 定制 Bitcell 优化的 Ribbon 宽度 —— 全面增强 18A 节点芯片性能与设计潜力。

另外,18A 采用了 PowerVia 技术,以背侧供电走线替代前侧走线,实现供电网络解耦与独立优化,从而实现多重增益:

逻辑密度提升

标准单元利用率改善

信号 RC 值降低

电压降(droop)收缩

设计灵活性进一步实现拓展

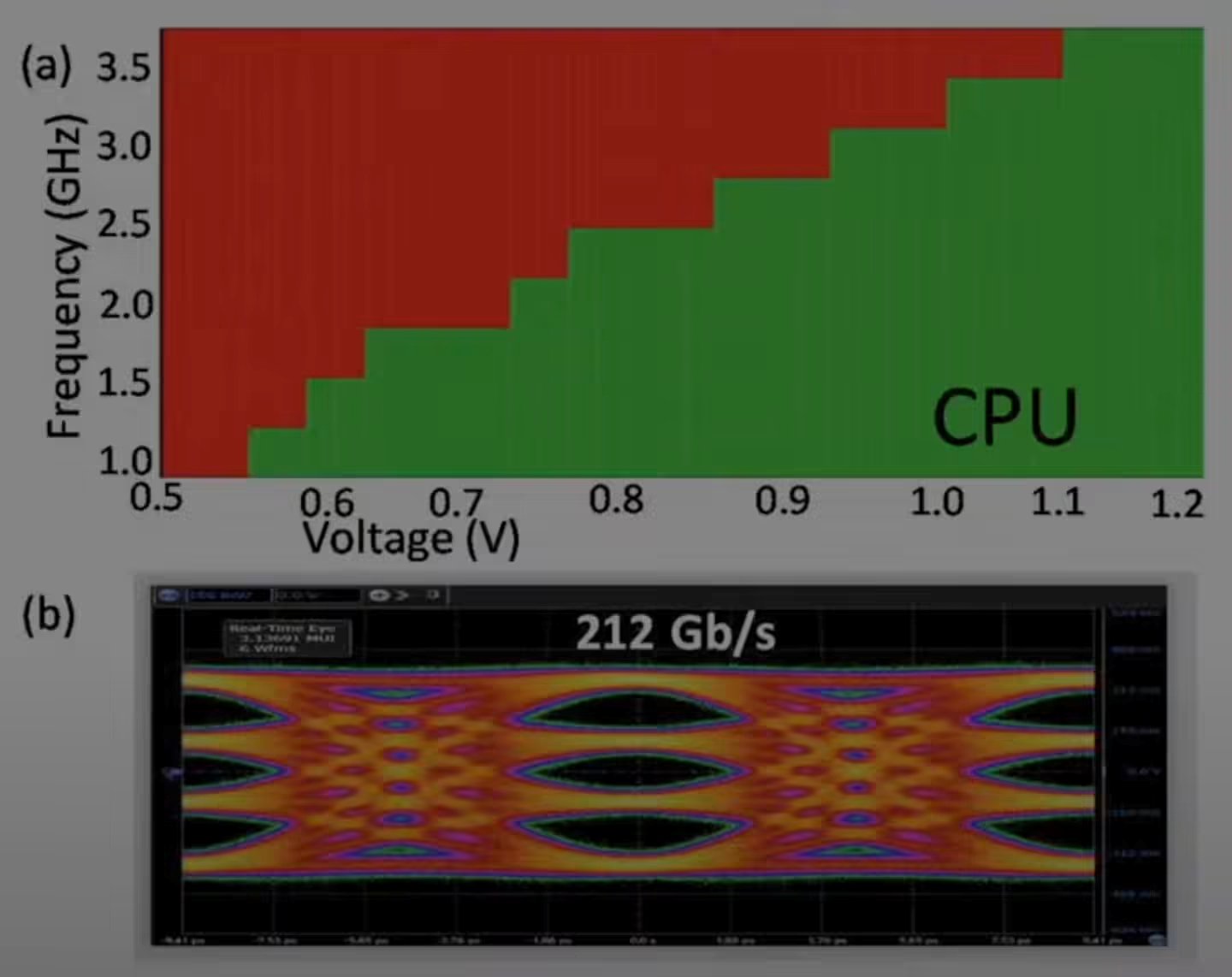

通过这些改进,Intel 18A 相比 Intel 3 实现了超过 15% 的单位功耗性能提升:

性能能效:1.1V 电压下,18A 同频性能较 Intel 3 提升约 25%;且支持 0.65V 以下低电压运行,同频功耗最多降 38%。

密度提升:18A 较 Intel 3 最高实现 39%(平均 30%)密度提升,背侧供电使单元利用率提 8-10%,单元利用率提高 8-10%,并将极端 IR 电压降收缩至原来的 10%。

参数对比:HP 库高度从 Intel 3 的 240nm 降至 180nm,HD 库从 210nm 降至 160nm;M0 / M2 金属层间距从 30/42nm 优化为 32/32nm。

SRAM 缩放:18A 的高电流单元(HCC)密度较 Intel 3 提升 30%,HCC、HDC SRAM 面积分别达 0.0230μm²、0.0210μm²。

英特尔表示,18A 工艺将持续迭代:2026-2028 年将推出 18A-P 和 18A-PT 衍生版本,并开放客户基于这些节点实现芯片量产。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。