双版本18A!英特尔发力新赛道

英特尔公布了其期待已久的18A制程节点的两个变体,使其更适合于,其一,制造面向大众市场的处理器;其二,制造用于人工智能(当然)的复杂多芯片半导体。

18A制程节点在2021年年中首次被提及,这个近似于2纳米的制程节点终于将于今年晚些时候随着英特尔Panther Lake客户端处理器系列的推出而进入量产阶段。然而,这个制程节点原本只是真正适用于专业高性能应用场景,比如高端中央处理器和图形处理器,而英特尔即将推出的14A制程节点才将是这家芯片制造商首个真正面向大众市场的制程节点。

遗憾的是,尽管14A制程节点有望实现每瓦性能提升15%到20%,但距离量产仍需几年时间。

面对日益增长的需求,尤其是对美国本土制造的芯片的需求,英特尔决定需要更快地推出一些产品来满足大众的需求,于是对其最初的18A制程进行了调整,推出了两个新的版本:一个版本旨在满足广泛的应用需求,另一个版本则是为多芯片人工智能加速器而优化的。

其中第一个版本被称为18A-P,它承诺比基础的18A制程节点每瓦性能再提升8%。更重要的是,对于已经在评估18A制程设计的客户,英特尔首席全球运营官纳加·钱德拉塞卡兰(Naga Chandrasekaran)称,向这个更新的制程节点过渡应该是无缝衔接的。

另一个变体被称为18A-PT,它针对需要硅通孔(TSV)的设计进行了优化。硅通孔技术允许通过硅进行通信和供电,这意味着芯片可以通过相互堆叠的方式进行组装。

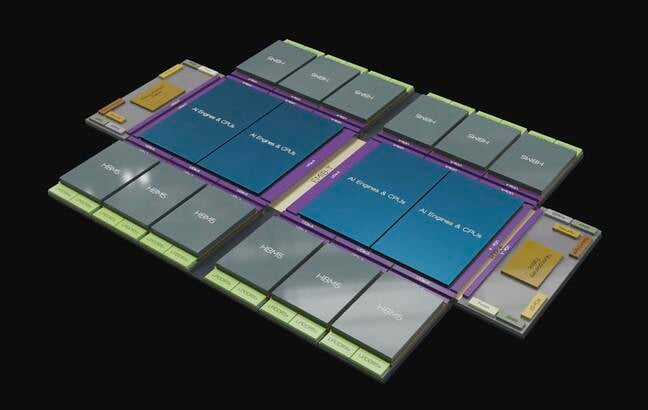

在周二举行的英特尔Foundry Direct Connect 2025活动上,英特尔铸造厂高级副总裁兼总经理凯文·奥布赖恩(Kevin O'Buckley)展示了一款概念性的人工智能加速器。该加速器将大量高速静态随机存取存储器(SRAM)芯片层夹在一个人工智能加速器或CPU芯片与一个基于18A-PT制程的基础芯片之间。

他解释道:“这就是我们的客户告诉我们他们需要我们为他们提供的东西。这是一种3D结构,有多个充分利用的基础掩模版芯片,上面堆叠着许多计算芯片。它周围环绕着超大容量的内存,既有性能最高的高带宽内存,在这种情况下,也有低功耗双倍数据速率芯片。并且这些都通过具有数十太比特带宽的电气和光学接口实现了连贯连接。我们相信,根据客户告诉我们的情况,在整个行业中,我们处于独特的位置,能够提供这些大规模的异构系统级封装。”

如果这听起来极其复杂且风险很大,要知道提出这种设计方案的并不只有英特尔。AMD和台积电都使用了先进的封装技术以及硅通孔技术,以提升计算密度或静态随机存取存储器的容量,这是传统制造技术难以实现的。

事实上,英特尔的这个概念让我们觉得它像是AMD的MI300X以及热那亚-X(Genoa-X)CPU和GPU的混合体。

或许更重要的是,英特尔凭借其嵌入式多芯片互连桥(EMIB)和“堆叠式芯片”(Foveros)技术,在2.5D和3D封装方面已经积累了相当丰富的经验,并且在其代号为“蓬齐奥·韦基奥”(Ponte Vecchio)的上一代数据中心GPU中广泛应用了这些技术。

钱德拉塞卡兰解释说,由于大多数人工智能加速器都需要先进的封装技术,英特尔现在正采取措施,将这些封装技术扩展应用到那些需要以更低成本获得大量计算能力和内存的客户设计中。

为此,该公司宣布与芯片封装和测试供应商Amkor展开合作,以便将其制造技术提供给更广泛的客户群体。英特尔与安靠科技的合作并不令人意外,因为台积电也在与安靠科技合作,以便在美国市场推出其晶圆级封装(CoWoS)技术。

陈立武的代工战略初具雏形

周二宣布的这些进展反映了新上任的首席执行官陈立武(Lip-Bu Tan)致力于实现其前任帕特·盖尔辛格(Pat Gelsinger)的愿景,即让英特尔成为一家为他人代工的芯片制造商并将其愿景变为现实。但与2024年英特尔铸造厂活动上提出的那些充满抱负的承诺不同,今年的活动务实得多。

陈立武没有宣称要超越三星电子的铸造厂市场份额,而是阐述了英特尔如何清除其铸造厂服务被采用过程中的障碍,如何建立客户对其制程和封装技术的信任,以及如何努力重新夺回制程技术领先地位。

陈立武表示:“这确实是一项服务业务,它建立在信任这一基本原则之上,而且你必须要有耐心才能赢得客户的信任。”他还补充说,英特尔必须提供符合客户期望的性能、可靠性和良率。

很明显,这一计划的一个关键方面涉及利用特朗普政府推动美国制造业发展所激发的对美国本土制造半导体的需求。

陈立武指出:“我们是唯一一家在美国进行先进的前沿半导体研发和制造的公司。”

然而,并非只有英特尔一家公司在美国制造前沿芯片,因为台积电已经在美国本土生产3纳米制程的芯片了。

本文转自媒体报道或网络平台,系作者个人立场或观点。我方转载仅为分享,不代表我方赞成或认同。若来源标注错误或侵犯了您的合法权益,请及时联系客服,我们作为中立的平台服务者将及时更正、删除或依法处理。